## AS2- OPÉRATIONS ET PORTES LOGIQUES

### EXERCICE 2-1

Les lignes des 3 premières colonnes du tableau suivant contiennent les  $2^3 = 8$  triplets de  $\mathcal{B}^3$ .

Pour  $y_1 = a + (b \cdot c)$  et  $y_2 = (a+b) \cdot (a+c)$ , démontrer de nouveau la distributivité de l'addition par rapport à la multiplication en remplissant les deux dernières colonnes du tableau.

| a | b | c | $y_1$       | $y_2$               |

|---|---|---|-------------|---------------------|

| 0 | 0 | 0 | $0+(0) = 0$ | $(0) \cdot (0) = 0$ |

| 0 | 0 | 1 | $0+(0) = 0$ | $(0) \cdot (1) = 0$ |

| 0 | 1 | 0 | $0+(0) = 0$ | $(1) \cdot (0) = 0$ |

| 0 | 1 | 1 | $0+(1) = 1$ | $(1) \cdot (1) = 1$ |

| 1 | 0 | 0 | $1+(0) = 1$ | $(1) \cdot (1) = 1$ |

| 1 | 0 | 1 | $1+(0) = 1$ | $(1) \cdot (1) = 1$ |

| 1 | 1 | 0 | $1+(0) = 1$ | $(1) \cdot (1) = 1$ |

| 1 | 1 | 1 | $1+(1) = 1$ | $(1) \cdot (1) = 1$ |

### EXERCICE 2-2

Montrer que

$$ab + ac + \bar{c}b = ac + \bar{c}b.$$

$$S = ab + ac + \bar{c}b = ab(c + \bar{c}) + ac + \bar{c}b$$

$$\text{Or } abc + ac = ac \text{ et } ab\bar{c} + \bar{c}b = \bar{c}b$$

$$\Rightarrow S = ac + \bar{c}b.$$

### EXERCICE 2-3

Montrer que

$$ab + c\bar{a} + \bar{c} + c\bar{b} = 1.$$

$$S = ab + c\bar{a} + \bar{c} + c\bar{b}$$

$$\text{Or exer 2-2} \Rightarrow ab + c\bar{a} = ab + c\bar{a} + bc$$

$$\text{mais } bc + c\bar{b} = c \text{ et } c + \bar{c} = 1$$

$$\Rightarrow S = ab + c\bar{a} + 1 = 1.$$

### EXERCICE 2-4

Montrer que NOR est aussi universelle.

$$\bar{a} = \overline{a+a} = a \downarrow a = \downarrow a,$$

$$a+b = \overline{\overline{a+b}} = \downarrow(a \downarrow b),$$

$$ab = \overline{\overline{a}\overline{\overline{b}}} = (\downarrow a) \downarrow (\downarrow b).$$

### EXERCICE 2-5

a) L'opération NAND (resp. NOR)

- 1) est-elle commutative ? associative ?

- 2) Admet-elle un élément neutre ? un élément absorbant ?

- 3) Est-elle distributive par rapport à «+» ou à «•» ?

Si la réponse est affirmative donner sa démonstration, si elle ne l'est pas trouver un contre-exemple.

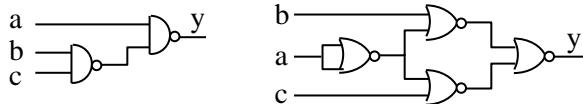

b) Représenter le circuit en portes NAND (resp. NOR) qui produit  $y = \bar{a} + bc$ .

a)

Commutatives car

$$a/b = \overline{ab} = \overline{ba} = b/a,$$

$$a \downarrow b = \overline{a+b} = \overline{b+a} = b \downarrow a$$

Non associatives car

$$1/(0/0) = \overline{1.(0.0)} = 0$$

$$\neq (1/0)/0 = \overline{(1.0).0} = 1.$$

$$1 \downarrow (0 \downarrow 0) = \overline{1+(0+0)} = 0$$

$$\neq (1 \downarrow 0) \downarrow 0 = \overline{(1+0)+0} = 1.$$

N'admettent pas un élément neutre ni absorbant car

$$a/0 = \overline{a.0} = 1, \quad a/1 = \overline{a.1} = \bar{a}$$

$$a \downarrow 1 = \overline{a+1} = 0, \quad a \downarrow 0 = \overline{a+0} = \bar{a}.$$

Non distributives par rapport à + ni à • car

$$1/(1+0) = \overline{1.(1+0)} = 0$$

$$\neq 1/1+1/0 = \overline{1.1} + \overline{1.0} = 1,$$

$$1/(1.0) = \overline{1.(1.0)} = 1$$

$$\neq 1/1.1/0 = \overline{1.1} \overline{1.0} = 0.$$

$$0 \downarrow (1+0) = \overline{0+(1+0)} = 0$$

$$\neq 0 \downarrow 1 + 0 \downarrow 0 = \overline{0+1} + \overline{0+0} = 1,$$

$$0 \downarrow (1.0) = \overline{0+(1.0)} = 1$$

$$\neq (0 \downarrow 1).(0 \downarrow 0) = \overline{0+1} \overline{0+0} = 0.$$

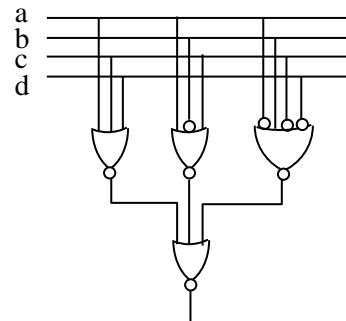

b)

$$\begin{aligned} y &= \bar{a} + bc = \overline{\bar{a} \cdot bc} = a / (b / c) \\ &= (\bar{a} + b) \cdot (\bar{a} + c) = \overline{\overline{\bar{a}} + b + \overline{\bar{a}} + c} = (\bar{a} \downarrow b) \downarrow (\bar{a} \downarrow c). \end{aligned}$$

**EXERCICE 2-6**

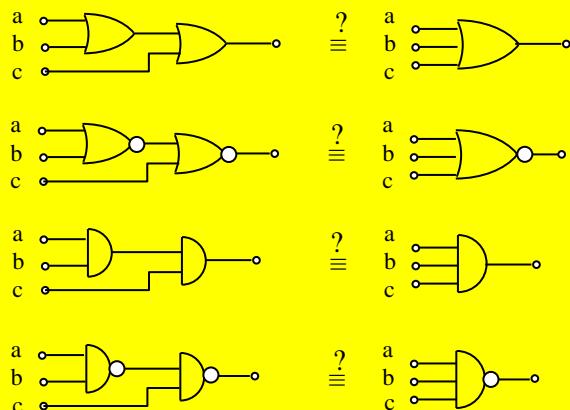

Les équivalences suivantes sont-elles toutes vraies ? Justifier votre réponse.

Les équivalences 1 et 3 sont vraies car « + » et « • » sont associatives. Les équivalences 2 et 4 sont fausses car « / » et « ↓ » ne sont pas associatives (voir exercice 2-5).

**EXERCICE 2-7**

- a) Démontrer l'associativité de  $\otimes$  et la distributivité de « • » par rapport à  $\oplus$ .

b) Partant seulement des propriétés 1) à 6) de XOR et de XNOR, montrer que  $a \oplus \bar{a} = 1$  et  $a \otimes \bar{a} = 0$ .

a)

$$\begin{aligned} a \otimes (b \otimes c) = 1 &\Leftrightarrow (a = 1 \text{ et } b = c) \text{ ou } (a = 0 \text{ et } b \neq c) \\ &\Leftrightarrow \text{nombre des 1 est impair} \\ &\Leftrightarrow (a \otimes b) \otimes c = 1. \end{aligned}$$

b)

$$\begin{aligned} a \oplus \bar{a} &= a \oplus (a \oplus 1), \quad 1\text{-inverseur} \\ &= (a \oplus a) \oplus 1, \quad \text{associativité} \\ &= 0 \oplus 1 = 1, \quad \text{a symétrique de } a \text{ et } 0 \text{ neutre.} \end{aligned}$$

$$\begin{aligned} a \otimes \bar{a} &= a \otimes (a \otimes 0), \quad 0\text{-inverseur} \\ &= (a \otimes a) \otimes 0, \quad \text{associativité} \\ &= 1 \otimes 0 = 0, \quad \text{a symétrique de } a \text{ et } 1 \text{ neutre.} \end{aligned}$$

**EXERCICE 2-8**

Montrer que

$$\begin{aligned} a_1 \otimes a_2 \otimes \dots \otimes a_p &= \text{XOR}(a_1, a_2, \dots, a_p) \text{ si } p \text{ impair,} \\ &= \text{XNOR}(a_1, a_2, \dots, a_p) \text{ si } p \text{ pair.} \end{aligned}$$

On sait que

$$\text{XOR}(a_1, a_2, \dots, a_p) = 1 \Leftrightarrow \text{nombre des 1 impair},$$

$$\text{XNOR}(a_1, a_2, \dots, a_p) = 1 \Leftrightarrow \text{nombre des 1 pair}.$$

$$\text{Or } a_1 \otimes a_2 = 1 \Leftrightarrow \text{nombre des 1 pair}$$

$$\Leftrightarrow a_1 \otimes a_2 = \text{XNOR}(a_1, a_2).$$

$$a_1 \otimes a_2 \otimes a_3 = 1 \Leftrightarrow \text{nombre des 1 impair (exr. 2-7)}$$

$$\Leftrightarrow a_1 \otimes a_2 \otimes a_3 = \text{XOR}(a_1, a_2, a_3).$$

La propriété est donc vraie pour  $p = 2$  et  $p = 3$ . Admettons qu'elle est vraie jusqu'à  $p - 1$  et montrons qu'elle reste vraie jusqu'à  $p$ .

$$\text{Posons } A_k = a_1 \otimes a_2 \otimes \dots \otimes a_k$$

$$\text{et } n_k = \text{nombre des 1 dans } A_k.$$

$$A_{p-1} = 1 \Leftrightarrow \begin{cases} n_{p-1} \text{ est impair si } p \text{ pair} \\ n_{p-1} \text{ est pair si } p \text{ impair} \end{cases} \text{ et } a_p = 1$$

$$\Leftrightarrow \begin{cases} n_p \text{ est pair si } p \text{ pair,} \\ n_p \text{ est impair si } p \text{ impair.} \end{cases} \Leftrightarrow A_p = \begin{cases} \text{XNOR si } p \text{ pair,} \\ \text{XOR si } p \text{ impair.} \end{cases}$$

**EXERCICE 2-9**

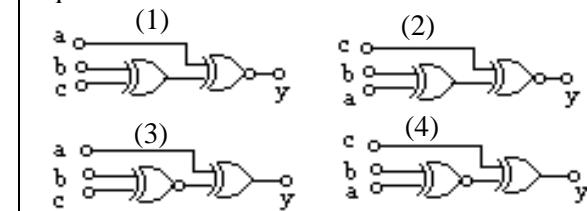

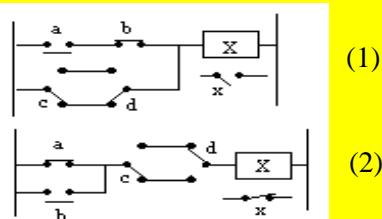

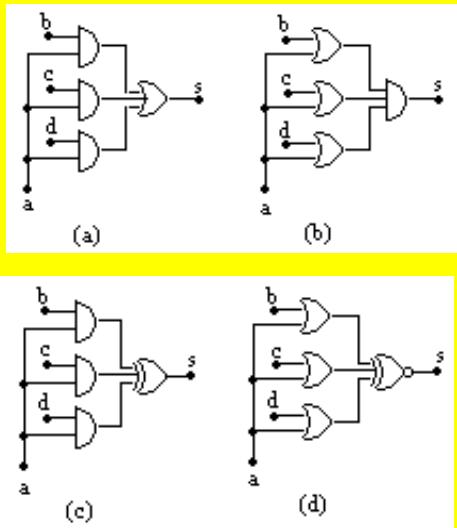

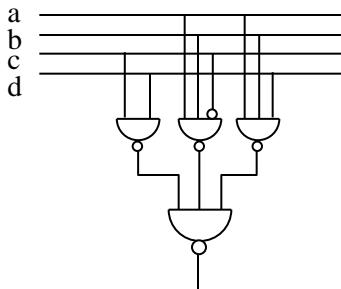

Montrer que les 4 circuits suivants sont équivalents.

$$\begin{aligned} (1) \Leftrightarrow y &= a \otimes (b \oplus c) = a(b\bar{c} + \bar{b}c) + \bar{a}(bc + \bar{b}\bar{c}) \\ &= c(ab + \bar{a}b) + \bar{c}(ab + \bar{a}\bar{b}) = c \otimes (b \oplus a) \Leftrightarrow (2) \\ &= a(bc + \bar{b}\bar{c}) + \bar{a}(bc + \bar{b}\bar{c}) = a \oplus (b \otimes c) \Leftrightarrow (3) \\ &= c(ab + \bar{a}b) + \bar{c}(ab + \bar{a}\bar{b}) = c \oplus (b \otimes a) \Leftrightarrow (4). \end{aligned}$$

**EXERCICE 2-10**

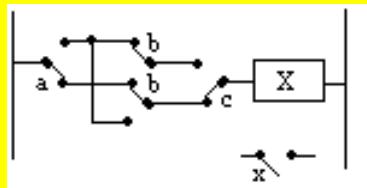

Les contacts b étant actionnés simultanément à l'aide d'une liaison mécanique, montrer que le circuit ci-dessous est une porte XNOR à trois entrées a, b et c. Quelle est l'utilité de ce circuit quand on remplace le relais par une lampe et les contacts a, b, c par des interrupteurs éloignés à l'intérieur d'une chambre.

Désignons par  $b_s$  la sortie supérieure du contact b et par  $b_i$  sa sortie inférieure. Le circuit montre que  $b_s = ab + \bar{a}\bar{b} = a \oplus b$  et  $b_i = \bar{a}\bar{b} + ab = a \otimes b$ .

$$\Rightarrow X = cb_s + \bar{c}b_i = c \oplus (a \otimes b) = c \otimes (a \otimes b)$$

Or, (exr 2-8),  $c \otimes (a \otimes b) = \text{XOR}(a, b, c)$

$$\Rightarrow x = X = \text{XNOR}(a, b, c).$$

Ce résultat peut être directement obtenu en remarquant que X s'active si et seulement si le nombre des contacts actionnés est pair (0 ou 2). En modifiant l'état d'un contact, la parité du nombre des contacts actionnés change ce qui change l'état de X = lampe.

**EXERCICE 2-11**

Montrer que les 2 circuits suivants sont équivalents.

$$(1) \Leftrightarrow x = ab + c \otimes d$$

$$(2) \Leftrightarrow x = (\bar{a} + b)(c \oplus d) = ab + c \otimes d.$$

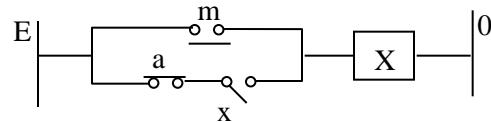

**EXERCICE 2-12**

Construire le circuit d'équation

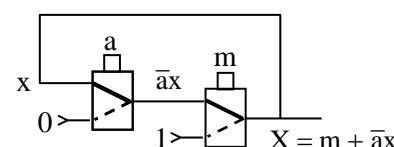

$X = m + \bar{a}.x$

et vérifier que c'est une mémoire à marche prioritaire.

Le circuit suivant réalise l'équation  $X = m + \bar{a}.x$ .

$$m = 1 \Rightarrow X = x = 1 \quad \forall a. \quad (1)$$

$$m = 0 \Rightarrow \begin{cases} x = 1 & \text{si } a = 0, \\ x = 0 & \text{si } a = 1. \end{cases}$$

(1) montre que  $m = a = 1 \Rightarrow X = 1$  donc la marche est prioritaire.

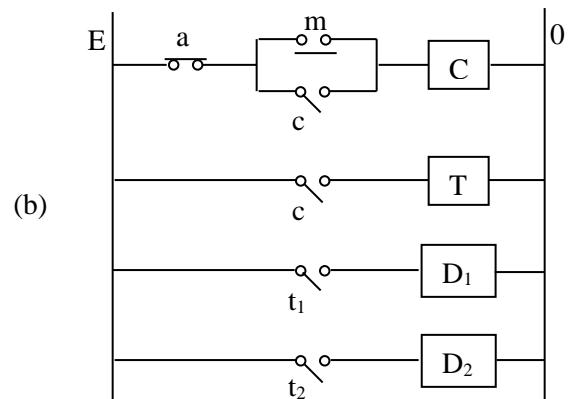

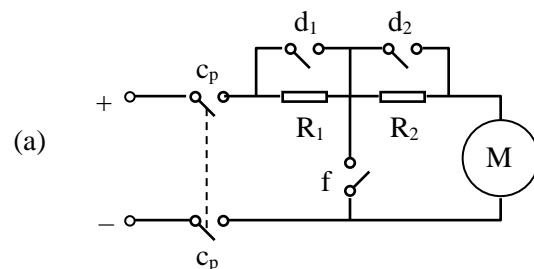

**EXERCICE 2-13**

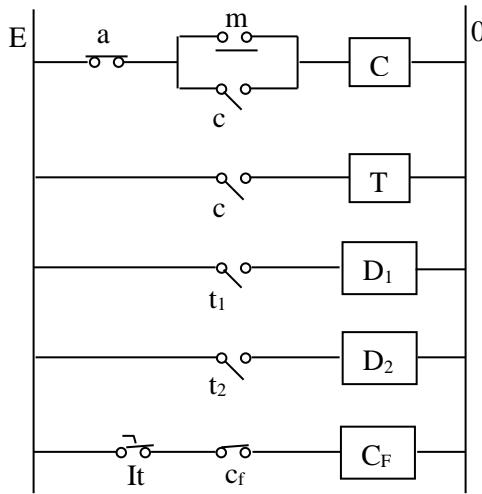

Le circuit (a) montre les organes de puissance connectés à un moteur cc pour effectuer un démarrage souple et un freinage rapide. Le circuit (b) est l'organe de commande pour le démarrage souple où T est un temporisateur à 2 pôles  $t_1$  et  $t_2$  de retards  $tr_1$  et  $tr_2 > tr_1$ .

Expliquer le fonctionnement de (b) et compléter le pour la commande du freinage rapide.

$d_1$  et  $d_2$  sont des pôles principaux respectivement des contacteurs  $D_1$  et  $D_2$ . Les  $c_p$  sont des pôles principaux du contacteur C et les autres pôles c sont auxiliaires.

En poussant sur le boutant de marche  $m$ , le contacteur  $C$  ferme ces pôles  $c_p$  et  $c$  pour alimenter le moteur à travers les résistances  $R_1$  et  $R_2$  et activer la mémoire et le temporisateur  $T$ . Après un temps  $t_{r1}$  le pôle  $t_1$  de  $T$  se ferme pour fermer le pôle  $d_1$  de  $D_1$  qui court-circuite la résistance  $R_1$  et alimente le moteur seulement à travers  $R_2$ . À l'instant  $t_{r2}$ , le pôle  $d_2$  se ferme à son tour pour que le moteur soit directement alimenté par le secteur.

En poussant sur le bouton d'arrêt  $a$ , on coupe le courant du contacteur  $C$  pour ouvrir tous ses pôles sauf un pôle auxiliaire  $c_f$  qui se ferme au repos pour alimenter un contacteur  $C_F$  et fermer un pôle principal  $f$ . L'énergie cinétique du moteur (qui devient générateur) se transforme en énergie calorifique qui se dissipe dans  $R_2$ . Pour obtenir ce freinage rapide, on ajoute au circuit de démarrage précédent une branche qui comporte le pôle  $c_f$ , le contacteur  $C_F$  et un interrupteur  $I_t$  qu'on ouvre après l'arrêt du moteur pour cesser d'alimenter  $C_F$ .

#### EXERCICE 2-14

Montrer que si les 2 sorties d'une cellule à 6 orifices sont toujours complémentaires quelles que soient les entrées, l'une est nécessairement un XOR et l'autre un XNOR.

Comment obtenir à l'aide d'une telle cellule les opérations NAND et NOR?

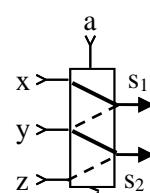

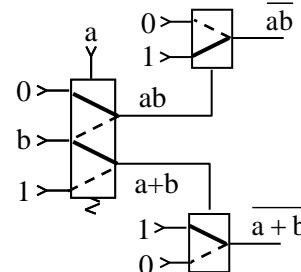

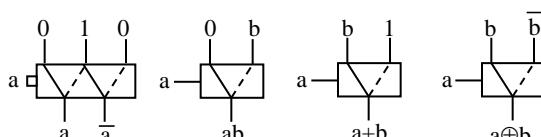

D'après le symbole d'une cellule à 6 orifices, les équations de ses sorties sont :

$$s_1 = \bar{a}x + ay \quad \text{et} \quad s_2 = \bar{a}y + az.$$

Si  $s_2 = \bar{s}_1$  quelles que soient les entrées, on a :

$$\begin{aligned} \bar{a}y + az &= \overline{\bar{a}x + ay} = (a + \bar{x})(\bar{a} + \bar{y}) \\ &= \bar{a}\bar{y} + \bar{a}\bar{x} + \bar{x}\bar{y} \quad \forall a, x, y, z \\ \Rightarrow z &= \bar{y} \quad \text{et} \quad y = \bar{x} \Rightarrow \bar{x}\bar{y} = y\bar{y} = 0 \\ \text{et } s_1 &= \begin{cases} \bar{a}\bar{y} + ay = a \otimes y \\ \bar{a}x + a\bar{x} = a \oplus x, \end{cases} \\ s_2 &= \begin{cases} \bar{a}y + a\bar{y} = a \oplus y \\ \bar{a}\bar{x} + ax = a \otimes x. \end{cases} \end{aligned}$$

À noter que le triplet  $(x, y, z)$  doit être de la forme  $(1, 0, 1)$  ou  $(0, 1, 0)$ .

Pour obtenir NAND et NOR, on connecte deux portes NOT à la cellule AND/OR.

#### EXERCICE 2-15

Construire une mémoire à marche prioritaire d'équation  $X = m + \bar{a}x$ .

On emploie une porte AND et une porte OR actionnés manuellement par les manettes  $a$  et  $m$ .

**EXERCICE 2-16**

On dispose d'un vérin à double effet alimenté à travers un distributeur à 3 positions (voir ch1, fig.1-50), de deux boutons de fin de course g et d actionnés par une came fixée à l'extrémité du piston et d'un bouton pneumatique m. Quand m = 0, le piston ne s'immobilise que si sa came touche d ou g. D'autre part, une impulsion sur m doit changer la direction de déplacement du piston quelle que soit la position de sa came entre d et g. Écrire les équations des signaux qui commandent le distributeur.

Le système peut être dans l'un des 3 états : déplacement à droite, déplacement à gauche et arrêt. Il faut 2 variables x et y pour coder ces états,

$$x = 1 \Leftrightarrow \text{déplacement à droite},$$

$$y = 1 \Leftrightarrow \text{déplacement à gauche}.$$

La mémoire de x se met en marche quand on pousse sur m en un moment où la came est en g ou elle se déplace vers la gauche après avoir quitté d. Quand m = 0, cette mémoire s'arrête en g et en d. Elle s'arrête quand elle arrive à d ou quand m = 1 en un moment où la came n'est pas en g. La valeur suivante de x est donc

$$\begin{aligned} X &= m(g + y\bar{d}) + \bar{m}(g + d) + m\bar{g} + d.x \\ &= m(g + y\bar{d}) + m \oplus g + d.x. \end{aligned}$$

Par symétrie, la valeur suivante de y est

$$Y = m(d + x\bar{g}) + m \oplus d + g.y$$

Les signaux de commande X et Y du distributeur sont les sorties de deux bascules d'entrées

$$S_x = m(g + y\bar{d}), \quad R_x = m \oplus g + d,$$

$$S_y = m(d + x\bar{g}), \quad R_y = m \oplus d + g.$$

Ces entrées s'obtiennent en combinant les portes à tiroir suivantes.

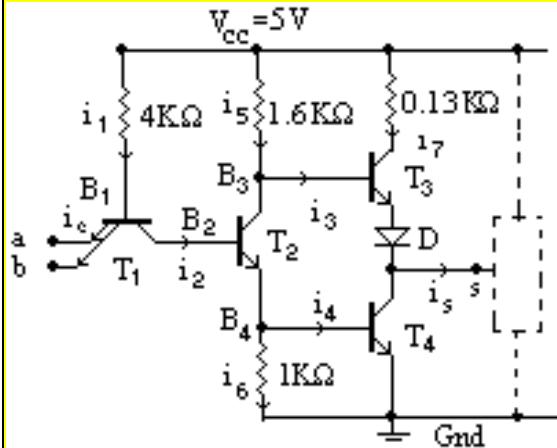

**EXERCICE 2-17**

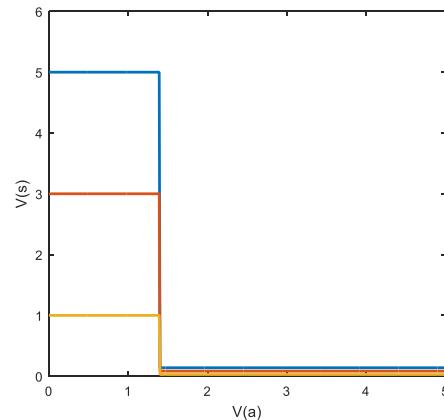

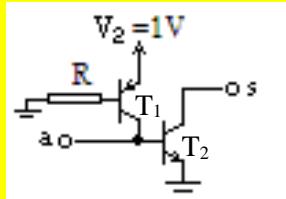

Pour  $V(b) = 5V$  et sachant que le gain des transistors du circuit NAND ci-dessous est  $\beta = 10$  et que leur tension de saturation est  $v_s = 1$

volt, estimer le courant de charge  $i_s$  dans les deux cas suivants:

a)  $V(a) = 0.8V, V(s) = 3V.$

b)  $V(a) = 2V, V(s) = 0.2V.$

a)

$$V(a) = 0.8V \Rightarrow T_2 \text{ et } T_4 \text{ bloqués.}$$

$$\begin{aligned} V(s) = 3V &\Rightarrow i_3 = (5 - 1.4 - 3)/1.6 = 0.375 \text{ mA} \\ \text{et } i_7 < (5 - 0.7 - 3)/0.13 &= 1.3 < \beta i_3 = 3.75 \text{ mA} \\ \Rightarrow T_3 \text{ saturé, d'où} & \end{aligned}$$

$$\begin{aligned} v_{ce} &= v_s(i_7/\beta i_3) \quad \text{et} \quad i_7 = (5 - v_{ce} - 0.7 - 3)/0.13 \\ \Rightarrow i_7 &= \left(1.3 - \frac{i_7}{3.75}\right)/0.13 \Rightarrow i_7 = 3.277 \text{ mA.} \end{aligned}$$

$$\text{Donc } i_s = i_7 + i_3 = 3.652 \text{ mA.}$$

b)

$$V(a) = 2V \Rightarrow T_2 \text{ et } T_4 \text{ passants} \Rightarrow B_1 = 2.1V$$

$$\Rightarrow i_2 = i_1 = (5 - 2.1)/4 = 0.725 \text{ mA.}$$

$$\begin{aligned} \text{Or } i_{c2} \leq i_5 < (5 - 0.7)/1.6 &= 2.69 < \beta i_2 = 7.25 \text{ mA} \\ \Rightarrow T_2 \text{ saturé.} & \end{aligned}$$

$$\Rightarrow v_{ce} = v_s(i_{c2}/\beta i_2) < 2.69/7.25 = 0.371 \text{ V}$$

$$\Rightarrow V(B_3) < 0.371 + 0.7 = 1.071 < 1.4$$

$\Rightarrow T_3$  bloqué.

D'autre part  $i_4 = i_5 + i_2 - i_6$ .

$$i_5 = (5 - v_{ce} - 0.7)/1.6 \text{ et } v_{ce} = v_s(i_5/\beta i_2)$$

$$\Rightarrow i_5 = (4.3 - i_5/7.25)/1.6 \Rightarrow i_5 = 2.47 \text{ mA.}$$

$$\Rightarrow i_4 = 2.47 + 0.725 - 0.7/1 = 2.5 \text{ mA}$$

$$\Rightarrow -i_s = \beta i_4 (V(s)/v_s) = 25(0.2) = -5 \text{ mA.}$$

**EXERCICE 2-18**

Que deviennent en logique opposée les portes NOR, AND, OR, XOR et XNOR.

Désignons par  $P_n$  ce que devient en logique négative une porte  $P$  en logique positive.  $P_n$  s'obtient à partir de  $P$  en complémentant ses entrées  $a$  et  $b$  et sa sortie  $s$ .

$$P = \text{NOR} \rightarrow P_n = \text{NAND} \quad \text{car}$$

$$\bar{s} = \overline{\bar{a} + \bar{b}} = ab \Rightarrow s = \overline{ab}$$

$$P = \text{AND} \rightarrow P_n = \text{OR} \quad \text{car}$$

$$\bar{s} = \overline{ab} = \overline{a + b} \Rightarrow s = a + b$$

$$P = \text{OR} \rightarrow P_n = \text{AND} \quad \text{car}$$

$$\bar{s} = \overline{a + b} = \overline{ab} \Rightarrow s = ab$$

$$P = \text{XOR} \rightarrow P_n = \text{XNOR} \quad \text{car}$$

$$\rightarrow \bar{s} = \overline{\bar{a} \cdot \bar{b} + \bar{a} \cdot b} = a \oplus b = a \otimes b$$

$$P = \text{XNOR} \rightarrow P_n = \text{XOR} \quad \text{car}$$

$$\bar{s} = \overline{a \cdot \bar{b} + ab} = a \otimes b = \overline{a \oplus b}.$$

### EXERCICE 2-19

Que donne la connexion des sorties de deux portes TTL ? Pourquoi faut-il l'éviter ?

En se référant au circuit de l'exercice 2-17, on constate que

$$s_1 = s_2 = 1$$

$\Rightarrow T_{41}$  et  $T_{42}$  bloqués.  $T_{31}$

et  $T_{32}$  passants

$\Rightarrow V(s)$  haute  $\Leftrightarrow s = 1$ .

$$s_1 \text{ ou } s_2 = 0$$

$\Rightarrow T_{41}$  ou  $T_{42}$  passant  $\Rightarrow V(s)$  basse  $\Leftrightarrow s = 0$ .

Donc  $s = s_1 \cdot s_2 \rightarrow \text{AND}$

Cette solution doit être évitée car si  $s_1 = 1$  et  $s_2 = 0$  c.à.d. si  $T_{31}$  et  $T_{42}$  sont passants, un courant élevé traverse et dissipe une chaleur excessive pouvant griller la porte. Évaluons cet échauffement en examinant le circuit de l'exercice 2-17. Comme  $V(s_1) \approx 0$ ,

$$i_3 = (5 - 1.4) / 1.6 = 2.25 \text{ mA} :$$

et comme  $i_7 < \beta i_3 = 22.5 \text{ mA}$ , la tension entre les bornes de  $T_{31}$  est

$$v_{ce} > 5 - 22.5(0.13) - 0.7 = 1.375 \text{ V}.$$

Le transistor n'est donc pas saturé et  $i_7 = \beta i_3 = 22.5 \text{ mA}$ . Le courant entre la source et la masse est  $i_3 + i_7 = 24.7 \text{ mA}$  qui dissipe une énergie calorifique  $W = 5(24.5) = 122.5 \text{ W}$ , beaucoup plus que ce qui est généralement admissible.

### EXERCICE 2-20

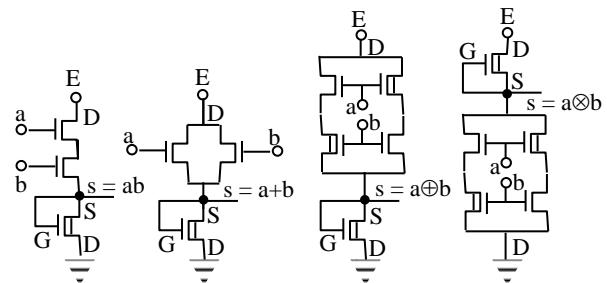

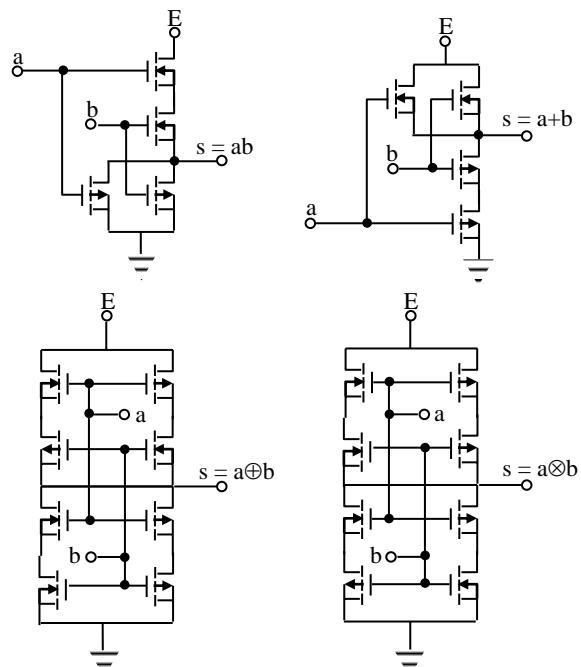

Concevoir en MOS et de la manière la plus simple les portes AND, OR, XOR et XNOR.

### EXERCICE 2-21

Concevoir en CMOS et de la manière la plus simple les portes AND, OR, XOR et XNOR.

### EXERCICE 2-21

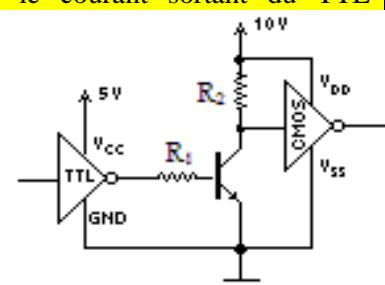

Choisir pour le circuit suivant les résistances  $R_1$  et  $R_2$  de sorte à saturer le transistor quand il est passant sans que le courant sortant du TTL dépasse  $10 \mu\text{A}$ .

On suppose que la tension de saturation de ce transistor est  $v_s = 1\text{V}$  et que son gain est  $\beta = 10$ .

À la sortie du TTL la tension est inférieure à 5V et le courant  $i_s$  doit être inférieur à 2mA. D'où

$$i_s \leq \frac{5 - 0.7}{R_1} \leq \frac{1}{100} \Rightarrow R_1 \geq 430 \text{ K}\Omega.$$

Le transistor devant se saturer quand il est passant, on a :

$$\begin{aligned} v_{ce} &= 10 - R_2 i_c < v_s = 1\text{V} \quad \text{avec } i_c = \beta i_s v_{ce} \\ \Rightarrow v_{ce} &= \frac{10}{(1 + \beta i_s R_2)} < 1 \Rightarrow R_2 > \frac{9}{\beta i_s} \geq \frac{9}{0.1} = 90 \text{ K}\Omega. \end{aligned}$$

### AUTRES EXERCICES ET COMPLÉMENTS

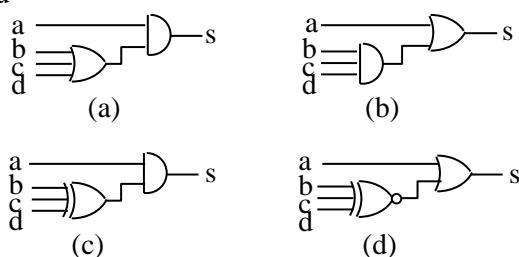

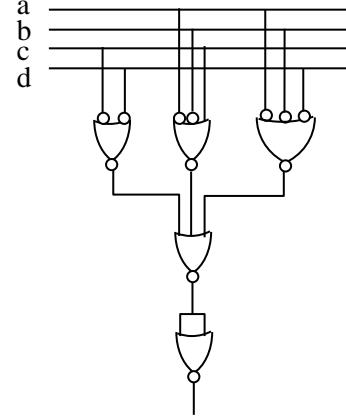

**2-22.** Remplacer chacun des circuits suivants par un circuit équivalent à deux portes.

$$\begin{aligned} (a) \rightarrow s &= ab + ac + ad = a(b + c + d) \quad \text{dist.} \cdot \% + \\ (b) \rightarrow s &= (a + b)(a + c)(a + d) = a + bcd \quad \text{dist.} + \% \cdot \\ (c) \rightarrow s &= ab \oplus ac \oplus ad = a(b \oplus c \oplus d) \quad \text{dist.} \cdot \% \oplus \\ (d) \rightarrow s &= (a + b) \otimes (a + c) \otimes (a + d) \\ &= a + (b \otimes c \otimes d) \quad \text{dist.} + \% \otimes. \end{aligned}$$

D'où

**2-23.** Le théorème de Shannon est une généralisation du théorème de De Morgan et s'énonce comme suit : *Le complément d'une expression logique comportant les opérateurs AND, OR, XOR, XNOR et NOT s'obtient en remplaçant chaque AND par un OR et chaque OR par un AND, chaque XOR par un XNOR et chaque XNOR par un XOR et en complémentant toutes les variables.*

- a) Vérifier ce théorème en déterminant les compléments des expressions suivantes :  $a + \bar{b} \cdot c$ ,  $a \oplus b$ ,  $a \oplus (\bar{b} \otimes c)$ ,  $(a + \bar{b}) \cdot c$ ,  $a \cdot (\bar{b} \oplus c) + d$ .

b) Appliquer ce théorème pour déterminer les compléments des expressions suivantes et vérifier chaque résultat à l'aide d'une table de vérité.

$(a + \bar{b}) \otimes c + \bar{a} \cdot (\bar{b} \oplus c)$ ,  $[(a + b) \oplus \bar{c}] \otimes [(\bar{a} + c) \oplus b]$

a)

$$\begin{aligned} \bullet a + \bar{b} \cdot c &= \bar{a}(b + \bar{c}) \quad \text{Morgan} \\ \bullet \overline{a \oplus b} &= a \otimes b = \bar{a}\bar{b} + ab = \bar{a} \otimes \bar{b}. \quad (1) \\ \bullet \overline{a \oplus (\bar{b} \otimes c)} &= \bar{a} \otimes \overline{(\bar{b} \otimes c)} = \bar{a} \otimes \overline{(b \otimes \bar{c})} \\ &= \bar{a} \otimes (b \oplus \bar{c}). \\ \bullet \overline{(a + \bar{b}) \cdot c} &= (a + \bar{b}) + \bar{c} = \bar{a}\bar{b} + \bar{c}. \\ \bullet \overline{\overline{a \cdot (\bar{b} \oplus c)} + d} &= \left[ \bar{a} + \overline{(\bar{b} \oplus c)} \right] \bar{d} = \left[ \bar{a} + (b \otimes \bar{c}) \right] \bar{d}. \end{aligned}$$

b)

$$\begin{aligned} X &= (a + \bar{b}) \otimes c + \bar{a} \cdot (\bar{b} \oplus c). \\ \bar{X} &= (\bar{a}\bar{b} \oplus \bar{c})[a + (\bar{b} \otimes \bar{c})] \\ Y &= [(a + b) \oplus \bar{c}] \otimes [(\bar{a} + c) \oplus b] \\ \bar{Y} &= (\bar{a}\bar{b} \otimes c) \oplus (a\bar{c} \otimes \bar{b}). \end{aligned}$$

| a | b | c | X | $\bar{X}$ |

|---|---|---|---|-----------|

| 0 | 0 | 0 | 0 | 1         |

| 0 | 0 | 1 | 1 | 0         |

| 0 | 1 | 0 | 1 | 0         |

| 0 | 1 | 1 | 0 | 1         |

| 1 | 0 | 0 | 0 | 1         |

| 1 | 0 | 1 | 1 | 0         |

| 1 | 1 | 0 | 0 | 1         |

| 1 | 1 | 1 | 1 | 0         |

| a | b | c | Y | $\bar{Y}$ |

|---|---|---|---|-----------|

| 0 | 0 | 0 | 1 | 0         |

| 0 | 0 | 1 | 0 | 1         |

| 0 | 1 | 0 | 1 | 0         |

| 0 | 1 | 1 | 0 | 1         |

| 1 | 0 | 0 | 1 | 0         |

| 1 | 0 | 1 | 0 | 1         |

| 1 | 1 | 0 | 0 | 1         |

| 1 | 1 | 1 | 0 | 1         |

**2-24.** Réaliser exclusivement en portes NAND les expressions suivantes :

$$f_1 = c \bar{d} + a.(b + \bar{c}) + \bar{a}.(d.\bar{b} + c),$$

$$f_2 = (a.b + c).(c \otimes d) + a.(b \oplus c).(d + \bar{c}).$$

a)

$$f_1 = \overline{\overline{f_1}} = \overline{(c \bar{d})} \cdot \overline{(ab)} \cdot \overline{(ac)} \cdot \overline{(adb)} \cdot \overline{(ac)}$$

b)

Dressons le tableau de Karnaugh de  $f_2$  espérant simplifier son expression.

$$\begin{aligned} f_2 &= (ab + c)(c \otimes d) + a(b \oplus c)(d + \bar{c}) \\ &= \underline{\underline{abcd}} + \underline{\underline{ab\bar{c}\bar{d}}} + cd + a(\underline{\underline{b\bar{c}d}} + \underline{\underline{b\bar{c}}} + \underline{\underline{\bar{b}cd}}) \\ &= acd + ab\bar{c} + cd. \end{aligned}$$

En ajoutant le terme de jonction  $abd$ , l'expression simplifiée de  $f_2$  est donc

$$\begin{aligned} f_2 &= cd + ab\bar{c} + abd \\ &= \overline{\overline{f_2}} = \overline{(cd)} \cdot \overline{(ab\bar{c})} \cdot \overline{(abd)}. \end{aligned}$$

**2-25.** Réaliser exclusivement en portes NOR les expressions  $f_1$  et  $f_2$  de l'exercice précédent.

a) Commençons par dresser la table de vérité de  $f_1$ .

| a b c d | $f_1$ | a b c d | $f_1$ |

|---------|-------|---------|-------|

| 0 0 0 0 | 0     | 1 0 0 0 | 1     |

| 0 0 0 1 | 1     | 1 0 0 1 | 1     |

| 0 0 1 0 | 1     | 1 0 1 0 | 1     |

| 0 0 1 1 | 1     | 1 0 1 1 | 0     |

| 0 1 0 0 | 0     | 1 1 0 0 | 1     |

| 0 1 0 1 | 0     | 1 1 0 1 | 1     |

| 0 1 1 0 | 1     | 1 1 1 0 | 1     |

| 0 1 1 1 | 1     | 1 1 1 1 | 1     |

Ce tableau montre que  $\overline{f_1}$  est plus simple que  $f_1$ . On a :

$$\begin{aligned} \overline{f_1} &= \overline{a \cdot \bar{c} \cdot \bar{d}} + \overline{a \cdot b \cdot \bar{c}} + \overline{a \cdot \bar{b} \cdot c \cdot d} \\ &= \overline{\overline{a + c + d} + \overline{a + \bar{b} + c} + \overline{\bar{a} + b + \bar{c} + d}} \\ f_1 &= \overline{\overline{a + c + d} + \overline{a + \bar{b} + c} + \overline{\bar{a} + b + \bar{c} + d}}. \end{aligned}$$

b)

L'expression simplifiée de  $f_2$  obtenue à l'exercice précédent s'écrit :

$$\begin{aligned} f_2 &= \overline{\overline{c + \bar{d}} + \overline{\bar{a} + \bar{b} + c} + \overline{\bar{a} + \bar{b} + \bar{d}}} \\ &= \overline{\overline{\overline{c + \bar{d}}} + \overline{\overline{\bar{a} + \bar{b} + c}} + \overline{\overline{\bar{a} + \bar{b} + \bar{d}}}} \end{aligned}$$

**2-26.** En remarquant que toute expression à n variables logiques  $f(a_1, a_2, \dots, a_n)$  peut s'écrire sous la forme  $\bar{a}_1 f(0, a_2, \dots, a_n) + a_1 f(1, a_2, \dots, a_n)$ , montrer les égalités suivantes :

$$ab + a\bar{b}c = a(b + c)$$

$$a\bar{b} + ad + b\bar{d} + \bar{a}\bar{b} = a + b$$

$$(ab) \oplus b + (a \oplus c)\bar{c}b + abc = b$$

$$a(b \otimes c) + b(a \oplus c) + ab(d \otimes c) + ac\bar{b}d = a + bc$$

$$ab + a\bar{b}c = \bar{a}.0 + a(b + \bar{b}c) = a(b + c).$$

$$a\bar{b} + ad + b\bar{d} + \bar{a}\bar{b} = \bar{a}(b\bar{d} + b) + a(\bar{b} + d + b\bar{d})$$

$$= \bar{b}\bar{d} + \bar{a}\bar{b} + a\bar{b}\bar{d} = b\bar{d} + a + \bar{a}\bar{b} = b\bar{d} + a + b$$

$$= a + b.$$

$$(ab) \oplus b + (a \oplus c)\bar{c}b + abc = \bar{a}b + a(\bar{c}b + bc)$$

$$= (\bar{a} + a\bar{c} + ac)b = (\bar{a}c + ac)b = b.$$

$$a(b \otimes c) + b(a \oplus c) + ab(d \otimes c) + ac\bar{b}d$$

$$= \bar{a}bc + a(b \otimes c + b\bar{c} + bdc + b\bar{d}\bar{c} + cbd)$$

$$= \bar{a}bc + a(bc + \bar{c} + c + b\bar{d}\bar{c}) = \bar{a}bc + a$$

$$= a + bc.$$

**2-27.** Construire un circuit logique à 4 entrées, numérotées 1, 2, 3 et 4, dont la sortie s est égale à 1 si et seulement si la somme des numéros des entrées sous tension est divisible par 3 sans que l'entrée n° 3 soit la seule sous tension. Ce circuit ne doit comporter que 2 portes chacune à 2 entrées.

$$s = 1.2.\bar{3}.\bar{4} + 1.2.3.\bar{4} + \bar{1}.2.3.4 + \bar{1}.2.\bar{3}.4$$

$$= (1.\bar{4}).2 + (\bar{1}.4).2 = (1 \oplus 4).2$$

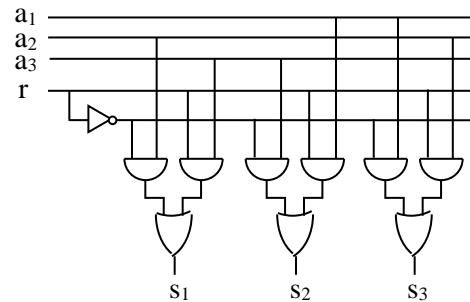

**2-28.** Soit r un signal logique. Construire un circuit qui associe au vecteur logique  $A = (a_1, a_2, a_3)$  sa rotation à droite,  $\vec{A} = (a_2, a_3, a_1)$ , si  $r = 0$ , sa rotation à gauche,  $\overleftarrow{A} = (a_3, a_1, a_2)$ , si  $r = 1$ .

Désignons par  $s_1, s_2, s_3$  les sorties du circuit. On a :

$$s_1 = \bar{r}a_2 + ra_3, \quad s_2 = \bar{r}a_3 + ra_1, \quad s_3 = \bar{r}a_1 + ra_2.$$

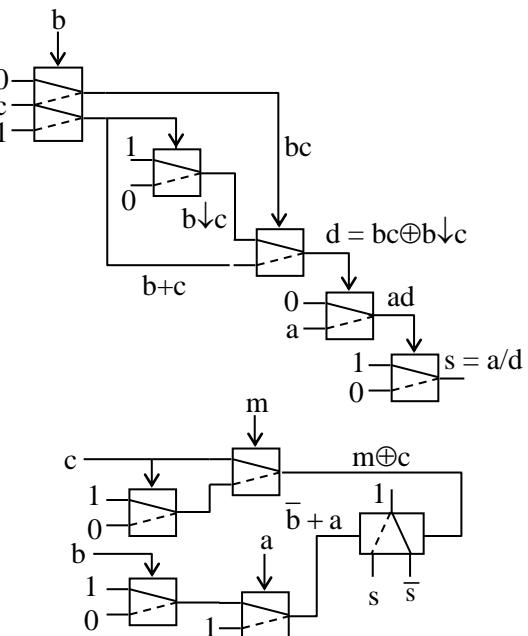

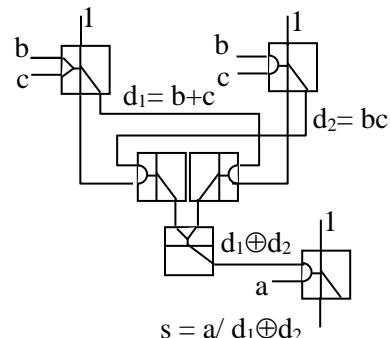

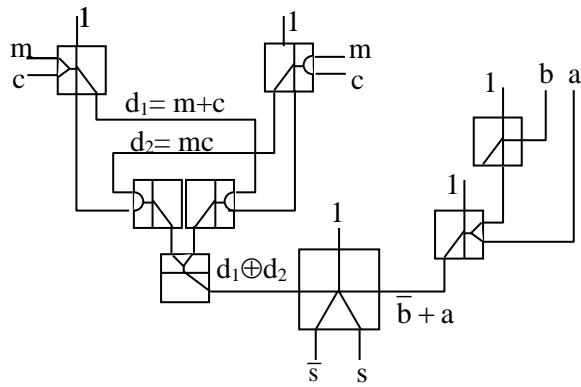

**2-29.** Construire pour chacune des expressions logiques suivantes un circuit pneumatique utilisant a) des cellules à tiroir, b) des cellules statiques:

$$s = a / [(b \downarrow c) \oplus b.c] \quad s = m \otimes c + s.(a.b).$$

a) Avec cellules à tiroir

b) Avec cellules statiques

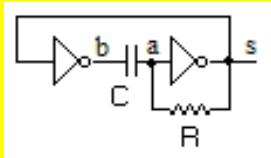

**2-30.** En supposant que la sortie d'un inverseur est égale à 5V si son entrée est inférieure à 1.4V et à 0V si son entrée est supérieure à 1.4V, montrer que le circuit suivant produit des impulsions périodiques à sa sortie s et déterminer en fonction de R et C la largeur de ces impulsions ainsi que leur fréquence.

Soit  $v_c = v_b - v_a$ . Durant  $v_s = c^{te} \Rightarrow v_b = c^{te}$ , on a :

$$\begin{aligned} v_a &= RC \frac{dv_c}{dt} + v_s = -RC \frac{dv_a}{dt} + v_s \\ \Rightarrow v_a(t) &= Ke^{-t/\tau} + v_s, \quad \tau = RC. \quad (1) \end{aligned}$$

En posant  $t = 0$  quand  $v_{bs}$  commute entre  $-5$  et  $+5V$  et sachant que la tension  $v_c(0^-)$  de la capacité juste avant la commutation est égale à sa tension  $v_c$  à la commutation, on a :

$$\begin{aligned} v_b(0^-) - 1.4 &= v_b(0) - v_a(0) = v_b - v_a(0) \\ \Rightarrow v_a(0) &= v_b - v_b(0^-) + 1.4. \end{aligned}$$

Comme la valeur précédente de  $v_b$  est égale à la tension actuelle en s c.à.d.  $v_b(0^-) = v_s(0) = v_s$ , on déduit de l'équation (1) que

$$K = v_b - 2v_s + 1.4 = \begin{cases} -8.6 & \text{si } v_s = 5V, \\ 6.4 & \text{si } v_s = 0V. \end{cases}$$

$$\text{Donc } v_a(t) = \begin{cases} -8.6e^{-t/\tau} + 5 & \text{si } v_s = 5V, \\ 6.4e^{-t/\tau} & \text{si } v_s = 0V. \end{cases}$$

Quand  $V_s = 5V$ ,  $V_a(t)$  croît de  $-3.6$  vers  $5$  en passant par  $1.4$  à l'instant  $t_1$  vérifiant

$$-8.6e^{-t_1/\tau} + 5 = 1.4 \Rightarrow e^{-t_1/\tau} = \frac{3.6}{8.6} \Rightarrow t_1 = 0.87\tau.$$

À l'instant  $t_1$ , où  $t$  redevient  $0$ ,  $v_s$  chute à  $0V$ .  $V_a(t)$  décroît de  $6.4$  vers  $0$  en passant par  $1.4$  à l'instant  $t_2$  vérifiant

$$6.4e^{-t_2/\tau} = 1.4 \Rightarrow e^{-t_2/\tau} = \frac{1.4}{6.4} \Rightarrow t_2 = 1.52\tau.$$

Période des oscillations :  $T = t_1 + t_2 = 2.39\tau$  sec

Fréquence :  $f = 1/T = 0.42/\tau$  Hz.

La figure suivante représente la fonction  $v_a(t)$  et le signal  $v_s$ .

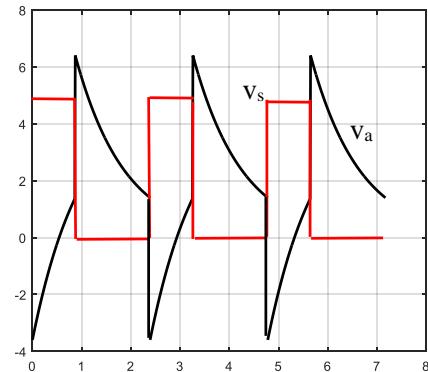

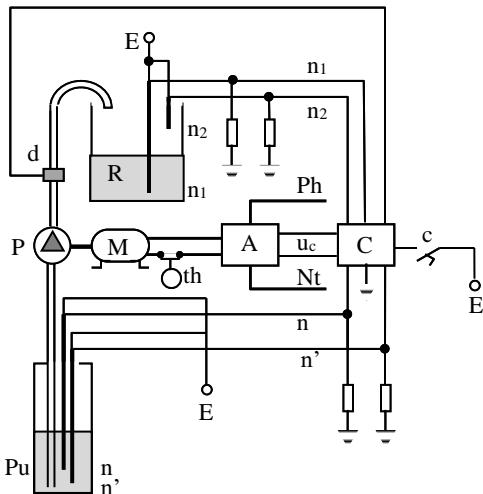

**2-31.** On désire alimenter par une pompe un réservoir d'eau à partir d'un puits. La pompe se met en marche si les conditions suivantes sont toutes satisfaites: a) le niveau d'eau dans le réservoir est inférieur à  $n_1$ , b) le niveau d'eau dans le puits est supérieur à  $n$  et c) un interrupteur c est fermé. Quand le relais thermique du moteur est fermé, la pompe s'arrête si l'eau dans le réservoir arrive à un niveau  $n_2$  ( $> n_1$ ) ou si l'eau dans le puits devient inférieur à un niveau  $n'$  ( $< n$ ). Enfin, un voyant s'allume et le courant du moteur se coupe si l'eau arrive au niveau  $n_1$  et que la pompe ne travaille pas. Utilisant des contacts de niveau à électrodes (voir ch.1 fig.8) et

sachant que le moteur de la pompe est alternatif monophasé, représenter pour ce réservoir le circuit électromagnétique et électronique de l'actionneur ainsi que le circuit électromagnétique de commande et de signalisation

### a) Structure du système

- L'objet commandé est la pompe P avec son moteur M.

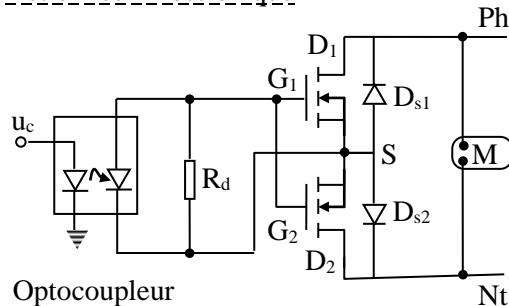

- A est l'actionneur alimenté par un courant alternatif entre une phase Ph et le neutre Nt. Il peut être électromagnétique ou électronique.

- Le transmetteur est constitué de 4 électrodes concentriques qui indiquent par des tensions E si le niveau d'eau dans le réservoir ou le puits a dépassé certaine valeur. Il comporte aussi un capteur de débit d qui indique si la pompe fonctionne ou non.

- En fonction des signaux du transmetteur et des contacts m et c l'organe de commande C agit sur l'actionneur par une tension de commande  $u_c$  pour mettre la pompe en marche ou l'arrêter.

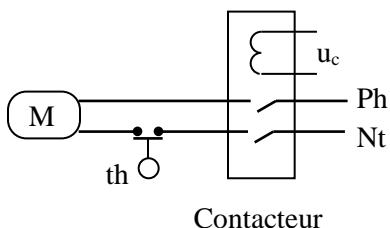

### b1) Actionneur électromagnétique

Le contacteur assure par l'induction de la bobine l'isolation galvanique entre l'organe de

commande C et l'actionneur A.

### b2) Actionneur Électronique

- L'isolation galvanique entre C et A est assurée par l'optocoupleur

- Durant l'alternance positive de la tension alternative, le courant passe par le MOS supérieur et la diode Ds2. Durant l'alternance négative, il passe par le MOS inférieur et la diode Ds1.

- Quand  $u_c$  s'annule, les grilles se déchargent à travers  $R_d$  et les transistors se bloquent pour couper le courant du moteur.

### c) Commande

Quand le niveau d'eau dans le réservoir est entre  $n_1$  et  $n_2$  la pompe peut se comporter de deux manières : si elle est en arrêt elle reste en arrêt et si elle est marche elle reste en marche (sauf si le niveau d'eau dans le puits devient plus bas que  $n'$ ). Il est donc nécessaire de mémoriser l'état x de la pompe par un circuit mémoire (pompe en marche,  $x = 1$ , en arrêt,  $x = 0$ ).

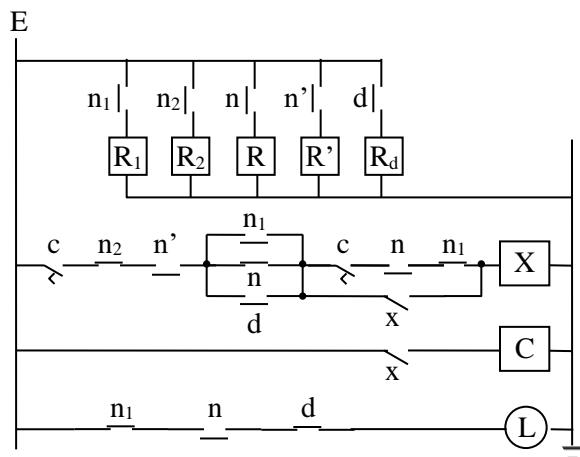

Le moteur de la pompe se met en marche au moment où  $c.n.\bar{n}_1$  devient 1 et ne s'arrête que lorsqu'on ouvre c ou  $n_2$  devient 1 ou  $n'$  s'annule ou  $\bar{n}_1 \bar{n} = 1$ . Cette dernière possibilité, qui signifie la présence d'un défaut, nous conduit à donner la priorité à l'arrêt et à allumer une lampe témoin L pour signaler la nécessité d'une réparation. Ainsi les équations de la mémoire X, du contacteur C et de la lampe L sont :

$$\begin{aligned} X &= \overline{\bar{c} + n_2 + \bar{n}' + \bar{n}_1 \bar{n}}(c.n.\bar{n}_1 + x) \\ &= \bar{c}\bar{n}_2 n'(n_1 + \bar{n} + d).(c.n.\bar{n}_1 + x). \\ C &= x \quad \text{et} \quad L = \bar{n}_1 \bar{n}. \end{aligned}$$

Ces équations se réalisent par le circuit de commande suivant. À noter que le contact

thermique arrête seulement le moteur quand son courant dépasse une certaine valeur sans affecter l'organe de commande ni le contacteur. Nous avons désigné les pôles des relais par les mêmes noms que leurs entrées.

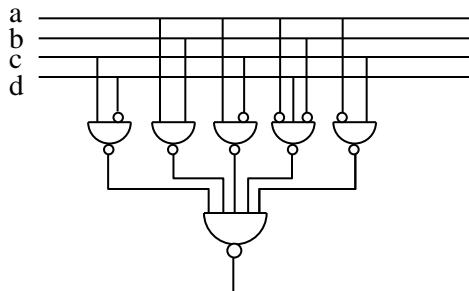

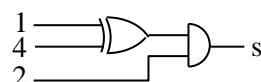

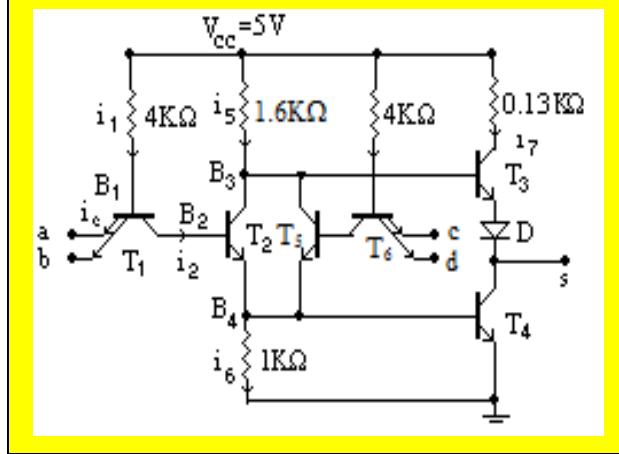

**2-32.** La figure suivante représente le circuit de la porte AND-OR-Inverter (AOI).

Écrire l'expression logique de la sortie s en fonction des entrées a, b, c et d. Construire une porte AOI en MOS et en CMOS.

a) Expression

$$s = 1 \Leftrightarrow T_1 \text{ et } T_2 \text{ bloqués} \Leftrightarrow ab = cd = 0$$

$$\Leftrightarrow ab + cd = 0.$$

$$s = 0 \Leftrightarrow T_1 \text{ ou } T_2 \text{ passant} \Leftrightarrow ab \text{ ou } cd = 1$$

$$\Leftrightarrow ab + cd = 1.$$

$$\text{Donc } s = \overline{ab + cd}.$$

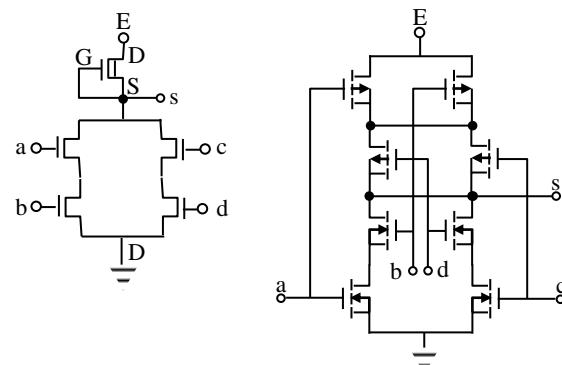

b) AOI en MOS et en CMOS

Il s'agit de construire l'inverse de deux AND en parallèle.

Le circuit CMOS est formé de 4 blocs A<sub>1</sub>, A<sub>2</sub>, B<sub>1</sub> et B<sub>2</sub>. Au-dessous de s, les blocs A<sub>k</sub>, k = 1 ou 2, sont parallèles, chacun est constitué de 2 MOS en série ouverts au repos et au-dessus de s, les blocs B<sub>k</sub> sont en série, chacun est constitué de 2 MOS en parallèle fermés au repos. Le bloc B<sub>k</sub> est le complément du bloc A<sub>k</sub> c.à.d. si l'un est passant l'autre est bloqué. Ainsi

$$s = 1 \Leftrightarrow A_1 \text{ et } A_2 \text{ bloqués} \Leftrightarrow ab = cd = 0$$

$$\Leftrightarrow ab + cd = 0.$$

$$s = 0 \Leftrightarrow A_1 \text{ ou } A_2 \text{ passant} \Leftrightarrow ab \text{ ou } cd = 1$$

$$\Leftrightarrow ab + cd = 1.$$

$$\text{Donc } s = \overline{ab + cd}.$$

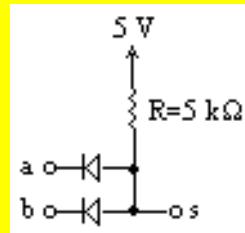

**2-33. Portes à diodes.**

1) Montrer que le circuit de la figure suivante est une porte AND. Construire une porte OR.

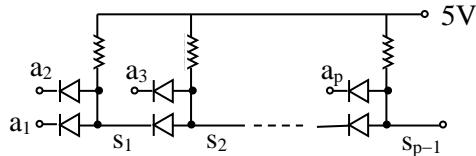

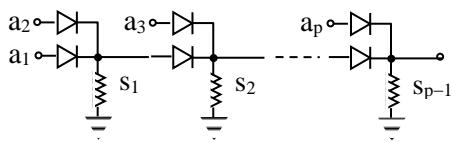

Convenons que le bit 1 correspond à une tension supérieure à 2.5 V et que le bit 0 correspond à une tension inférieure à 2.5 V et supposons qu'on désire réaliser l'expression a<sub>1</sub>.a<sub>2</sub>....a<sub>p</sub> à l'aide de portes AND à diodes chacune ayant 2 entrées. Quelle est la plus grande valeur de p.

2) Même question si l'on désire réaliser l'expression  $a_1 + a_2 + \dots + a_p$  à l'aide de portes OR à diodes chacune ayant 2 entrées.

1) Si  $a = 0$  ou  $b = 0$ , le courant traverse l'une des diodes et la tension en  $s$  sera égale à  $0.7V < 2.5V$  d'où la valeur logique de  $s$  est 0. Par contre, si  $a = 1$  et  $b = 1$  (5V), les deux diodes se bloquent, le courant à travers la résistance s'annule et la tension en  $s$  devient 5V (1 logique). Donc  $s = ab$ .

Le circuit ci-contre est une porte OR car si  $a = 1$  ou  $b = 1$  ( $5V$ ), la tension en  $s$  est  $5 - 0.7 = 4.3V > 2.5V$  et la valeur logique de  $s$  est 1. Cette valeur n'est nulle que si  $a = b = 1$ . Donc  $s = a + b$ .

2)

Si  $a_1 = a_2 = \dots = a_p = 1$ , toutes les diodes du circuit ci-dessus se bloquent, aucun courant ne peut traverser le circuit et la tension à la sortie  $s_{p-1}$  sera  $5V > 2.5V$  de valeur logique 1. Mais si  $a_1 = 0$ , toutes les diodes inférieures seront passantes d'où les tensions en  $s_1, s_2, \dots, s_{p-1}$  seront respectivement  $0.7V, 2(0.7)V, \dots, (p-1)(0.7)V$ . Par conséquent, la valeur logique de la sortie  $s_{p-1}$  ne sera égale à 0 que si  $(p-1)(0.7) < 2.5 \Rightarrow p < 2.5/0.7 + 1$  c.à.d.  $p$  ne doit pas dépasser 4.

2)

Si  $a_1 = a_2 = \dots = a_p = 0$ , toutes les diodes du circuit ci-dessus se bloquent, aucun courant ne peut traverser le circuit et la tension à la sortie  $s_{p-1}$  sera  $0V < 2.5V$  de valeur logique 0. Mais si  $a_1 = 1$  ( $5V$ ), toutes les diodes inférieures seront passantes d'où les tensions en  $s_1, s_2, \dots, s_{p-1}$

seront respectivement  $5 - 0.7V, 5 - 2(0.7)V, \dots, 5 - (p-1)(0.7)V$ . La valeur logique de la sortie  $s_{p-1}$  ne sera donc égale à 1 que si  $5 - (p-1)(0.7) > 2.5 \Rightarrow p < 2.5/0.7 + 1$  c.à.d.  $p$  ne doit pas dépasser 4.

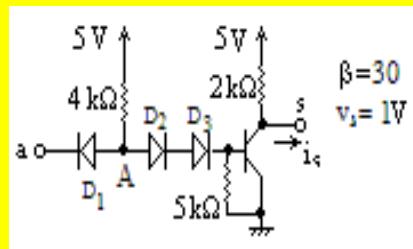

### 2-34. Diode-Transistor Logic (DTL).

Le circuit de la figure suivante fait partie de la famille DTL.

1) Montrer qu'il est un inverseur et dire comment le modifier pour obtenir une porte NAND.

2) Pour  $i_s = 0A$  (fonctionnement à vide), déterminer les courants dans les branches de l'inverseur ainsi que l'énergie dissipée dans cette porte dans les deux cas :  $V(a) = 0V$  et  $V(a) = 5V$ .

3) Quand  $V(a)$  varie entre 0 et 5V, représenter  $V(s)$  pour  $i_s = 0, 1$  et  $2\text{ mA}$ .

1) Quand  $a = 0V$ , la diode  $D_1$  est passante, la tension en  $A$  vaut  $0.7V < 3(0.7)$ , d'où les diodes  $D_2, D_3$  et le transistor se bloquent. Le courant à travers la résistance  $2k\Omega$  est donc nul et la tension en  $s$  vaut  $5V$  ( $s = 1$  logique). Quand  $a = 1$  ( $5V$ ), la diode  $D_1$  se bloque, un courant traverse la résistance  $4k\Omega$  et les diodes  $D_2$  et  $D_3$  pour débloquer le transistor et connecter  $s$  à la masse ce qui rend la tension en  $s$  voisine de  $0V$  ( $s = 0$  logique). Ces résultats montrent que  $s = \bar{a}$ .

Si, en parallèle à la diode  $D_1$  et l'entrée  $a$ , on branche une diode  $D_4$  avec une deuxième entrée  $b$ , le transistor ne sera passant et  $s$  ne sera égale à 0 (logique) que lorsque  $a = b = 1$ . Ceci signifie que  $s = ab$ .

2)

a)  $V(a) = 0V$

Un courant  $i_1 = (5 - 0.7)/4 = 1.075 \text{ mA}$  traverse la résistance  $4 \text{ k}\Omega$  et la diode  $D_1$  pour aboutir à la masse à travers l'entrée  $a$ , qui est connectée à la masse. Aucun autre courant ne traverse le circuit. L'puissance dissipée dans la porte est donc  $P_d = V_{cc}i_1 = 5(1.075) = 5.375 \text{ mW}$ .

b)  $V(a) = 5V$

Un courant  $i_b = [(5 - 3(0.7))/4] = 0.725 \text{ mA}$  traverse la résistance  $4 \text{ k}\Omega$ , les diodes  $D_2$  et  $D_3$ , pénètre dans la base du transistor pour aboutir à la masse à travers l'émetteur. Comme

$$\beta i_b = 30(0.725) = 21.75 > 5 / 2 > i_c,$$

Le transistor se sature et on a :

$$i_c = \beta i_b \frac{V_{ce}}{V_s} \quad \text{et} \quad V_{ce} = 5 - 2i_c$$

$$\Rightarrow i_c = \frac{5\beta i_b}{1 + 2\beta i_b} = \frac{5(21.75)}{1 + 2(21.75)} = 2.444 \text{ mA.}$$

Le courant de la source à la masse est alors

$$i_e = i_c + i_b = 2.444 + 0.725 = 3.169 \text{ mA}$$

et la puissance dissipée dans le transistor est  $P_d = 5(3.169) = 15.44 \text{ mW}$ .

3)

La diode  $D_1$  est passante si  $V(a) = V(A) - 0.7V$ . Or, à cause des diodes  $D_2$  et  $D_3$  et du transistor,  $V(A) \leq 2.1V$ . D'où la diode  $D_1$  n'est pas passante que si  $V(a) < 1.4V$  et dans ce cas  $V(A) < 1.4 + 0.7V$  ce qui bloque le transistor et la tension de sortie sera  $V(s) = 5 - 2i_s$ .

Quand  $V(a) \geq 1.4V$ ,  $D_1$  se bloque,  $V(A)$  prend la valeur  $2.1V$  et le courant  $i_b = [(5 - 2.1)/4 - 0.7/5] = 0.585 \text{ mA}$  débloque le transistor. Comme,

$$\beta i_b = 30(0.585) = 17.55 > 5 / 2 - i_s > i_c,$$

le transistor se sature et on a :

$$V(s) = V_{ce} = 5 - 2(\beta i_b \frac{V_{ce}}{V_s} + i_s)$$

$$\Rightarrow V(s) = \frac{5 - 2i_s}{1 + 2(17.55)}$$

Ainsi

$$V(s) = V_{ce} = \begin{cases} 5 - 2i_s & \text{si } V(a) < 1.4V, \\ \frac{5 - 2i_s}{36.1} & \text{si } V(a) \geq 1.4V. \end{cases}$$

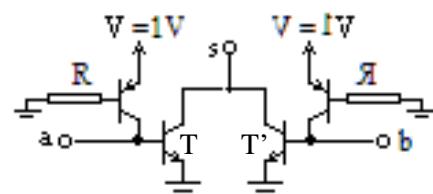

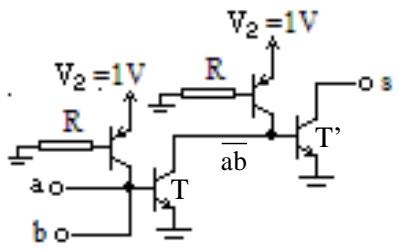

### 2-35. Integrated Injection Logic (I<sup>2</sup>L).

1) En convenant que l'entrée  $a$  ou la sortie  $s$  est égale à 1 si elle est flottante, à 0 si elle est voisine de 0V, quelle est la fonction logique du circuit de la figure suivante

2) Représenter le circuit d'une porte NOR et d'une porte AND en I<sup>2</sup>L.

1)  $s = 1 \Leftrightarrow T_2$  bloqué  $\Leftrightarrow$  Le coutant de  $T_1$  se dirige vers  $a \Leftrightarrow a = 0$ . Donc  $s = \bar{a}$  (porte NOT).

2) On obtient une porte NOR en connectant les sorties de deux inverseurs comme le montre la figure suivante.

En effet

$$s = 0 \Leftrightarrow T \text{ ou } T' \text{ passant} \Leftrightarrow a = 1 \text{ ou } b = 1 \Leftrightarrow a + b = 1.$$

$$\text{Donc } s = \overline{a + b}.$$

On obtient une porte AND en connectant la sortie d'une porte NAND à un inverseur comme le montre la figure suivante

En effet

$$\begin{aligned}s = 1 &\Leftrightarrow T' \text{ bloqué} \Leftrightarrow T \text{ passant} \Leftrightarrow a = 1 \text{ et } b = 1 \\&\Leftrightarrow ab = 1.\end{aligned}$$

Donc  $s = ab$ .