## AS5- CIRCUITS USUELS

### EXERCICE 5-1

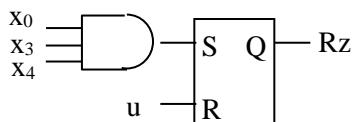

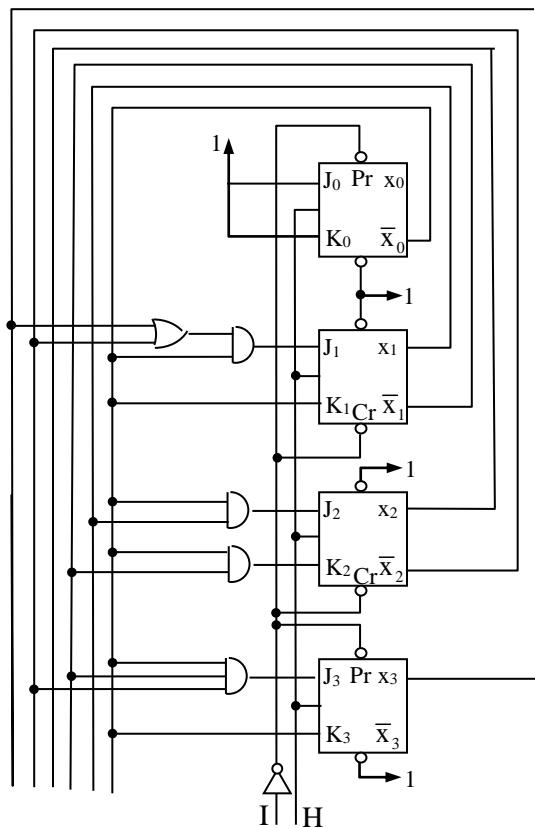

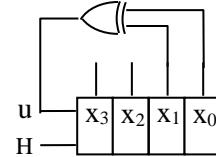

Représenter le circuit de remise à zéro d'un compteur modulo 25.

Dans  $B^5$ , l'écriture binaire de 25 est (1 1 0 0 1). C'est le plus petit entier pour lequel le premier, le quatrième et le cinquième bit sont égaux à 1. Pour obtenir un compteur modulo 25, on remet toutes les bascules à zéro à l'instant où le produit  $x_0x_3x_4$  devient 1. Le loquet SR maintient cette valeur 1 entre la dernière impulsion de l'entrée u du compteur et la suivante afin de donner aux sorties des bascules du compteur le temps de se stabiliser.

### EXERCICE 5-2

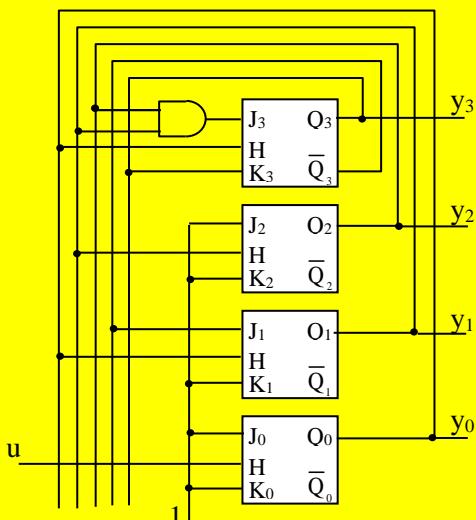

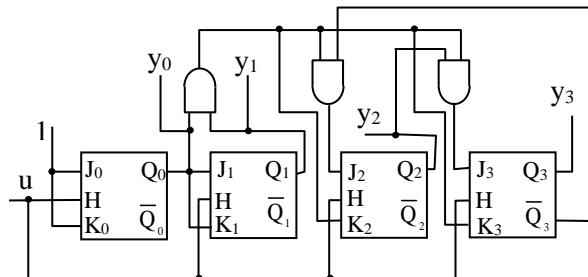

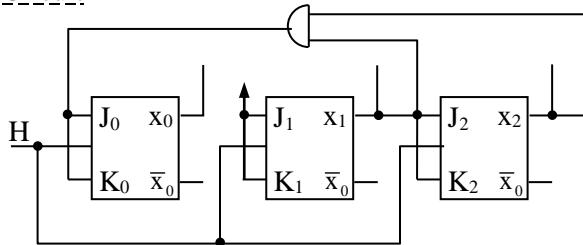

Vérifier que le circuit intégré 74LS90 ci-dessus est un compteur asynchrone modulo 10 qui ne comporte pas un circuit de remise à zéro.

Les 4 composantes de la réponse sont les sorties  $y_i$  des bascules JK. La valeur suivante de  $y_i$  est liée à la valeur actuelle et les entrées par l'équation

$$y'_i = J_i \bar{y}_i + \bar{K}_i y_i \quad (1)$$

déduite du tableau de vérité ci-contre de cette bascule. La valeur de  $y_i$  se modifie à la descente de l'entrée H de 1 à 0.

| K |   | J      |       |

|---|---|--------|-------|

| 0 | 0 | 1      | 1     |

| 1 | 0 | 0      | 1     |

|   |   | $y_i'$ | $y_i$ |

Le tableau suivant donne les sorties d'un compteur modulo 10 suite aux impulsions successives de l'entrée u.

| N° | $y_3y_2y_1y_0$ | N° | $y_3y_2y_1y_0$ |

|----|----------------|----|----------------|

| 0  | 0 0 0 0        | 5  | 0 1 0 1        |

| 1  | 0 0 0 1        | 6  | 0 1 1 0        |

| 2  | 0 0 1 0        | 7  | 0 1 1 1        |

| 3  | 0 0 1 1        | 8  | 1 0 0 0        |

| 4  | 0 1 0 0        | 9  | 1 0 0 1        |

|    |                | 0  | 0 0 0 0        |

On remarque que la sortie  $y_0$  change de valeur après chaque impulsion de l'entrée u. La nouvelle valeur  $y'_0$  de  $y_0$  devient donc le complément de sa valeur actuelle au front descendant (de 1 à 0) de u. D'où, d'après (1),

$$(u \downarrow), \quad y'_0 = \bar{y}_0 \Rightarrow J_0 = K_0 = 1.$$

Le bit  $y_1$  change de valeur à chaque descente de  $y_0$  sauf lorsque  $y_3 = 1$ , la valeur suivante de  $y_1$  sera 0 (voir les deux dernières cases du tableau).

D'où

$$(y_0 \downarrow), \quad y'_1 = \bar{y}_3 \bar{y}_1 \Rightarrow J_1 = \bar{y}_3, K_1 = 1.$$

Le bit  $y_2$  change de valeur à chaque descente de  $y_1$ . D'où

$$(y_1 \downarrow), \quad y'_2 = \bar{y}_2 \Rightarrow J_2 = K_2 = 1.$$

Enfin, en examinant les 4 dernières cases, on constate que  $y_3$  change de valeur à la descente de  $y_0$  si  $y_1 = y_2 = 1$  ou si  $y_3 = 1$ . D'où

$$(y_0 \downarrow), \quad y'_3 = y_1 y_2 \bar{y}_3 + y_3 \bar{y}_3 \Rightarrow J_3 = y_1 y_2, K_3 = \bar{y}_3.$$

Les 4 résultats précédents justifient la constitution du circuit.

### EXERCICE 5-3

Construire un compteur synchrone modulo 12.

Le tableau suivant donne en valeur décimale la réponse suivante  $y'$  en fonction de la réponse actuelle  $y$  d'un compteur modulo 12.

Tableau 1

|       | $y_0$ | $y_1$ |    |

|-------|-------|-------|----|

| $y_2$ | 1     | 2     | 4  |

| $y_3$ | 5     | 6     | 8  |

|       |       |       | 7  |

|       | 9     | 10    | 0  |

|       |       |       | 11 |

|       | $y'$  |       |    |

Par exemple, pour passer de  $y = 3 = (0\ 0\ 1\ 1)$  à  $y' = 4 = (0\ 1\ 0\ 0)$ , on complémente les valeurs de  $y_0$ ,  $y_1$  et  $y_2$  mais  $y_3$  maintient sa valeur précédente. Des bascules JK peuvent réaliser ces variations de la sortie du compteur. Après chaque impulsion de l'entrée u, les sorties des bascules JK se modifient selon la règle donnée par le tableau suivant.

| $y_i \rightarrow y'_i$ | $0 \rightarrow 0$ | $0 \rightarrow 1$ | $1 \rightarrow 0$ | $1 \rightarrow 1$ |

|------------------------|-------------------|-------------------|-------------------|-------------------|

| J K                    | 0 -               | 1 -               | - 1               | - 0               |

De cette règle et tenant compte du tableau 1 des transitions de  $y$  à  $y'$ , on déduit les tableaux des entrées  $J_i$  et  $K_i$  de la bascule relative au bit  $y_i$ ,  $i = 1, 2, 3$ , de la réponse. Comme  $y_0$  commute après chaque impulsion de  $u$ , ce bit est la sortie d'un trigger qu'on obtient en connectant  $J_0$  et  $K_0$  à la source de tension (à 1).

| $J_1$ | $y_0$ | $y_1$ |  |

|-------|-------|-------|--|

| $y_2$ | 0     | 1     |  |

| $y_3$ | 0     | 1     |  |

|       | 0     | 1     |  |

| $K_1$ | $y_0$ | $y_1$ |     |

|-------|-------|-------|-----|

| $y_2$ |       |       | 1 0 |

| $y_3$ |       |       | 1 0 |

|       |       |       | 1 0 |

| $J_2$ | $y_0$ | $y_1$ |     |

|-------|-------|-------|-----|

| $y_2$ | 0     | 0     | 1 0 |

| $y_3$ | 0     | 0     | 0 0 |

|       | 0     | 0     | 0 0 |

| $K_2$ | $y_0$ | $y_1$ |         |

|-------|-------|-------|---------|

| $y_2$ |       |       | 0 0 1 0 |

| $y_3$ |       |       | 0 0 1 0 |

|       |       |       | 0 0 1 0 |

| $J_3$ | $y_0$ | $y_1$ |     |

|-------|-------|-------|-----|

| $y_2$ | 0     | 0     | 0 0 |

| $y_3$ | 0     | 0     | 1 0 |

|       |       |       | 1 0 |

| $K_3$ | $y_0$ | $y_1$ |         |

|-------|-------|-------|---------|

| $y_2$ |       |       | 0 0 1 0 |

| $y_3$ |       |       | 0 0 1 0 |

|       |       |       | 0 0 1 0 |

De ces tableaux, on déduit les équations suivantes :

$$J_1 = y_0, \quad J_2 = y_0 y_1 \bar{y}_3, \quad J_3 = y_0 y_1 y_2.$$

$$K_1 = y_0, \quad K_2 = y_0 y_1, \quad K_3 = y_0 y_1.$$

#### EXERCICE 5-4

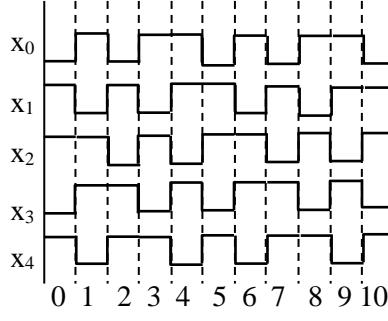

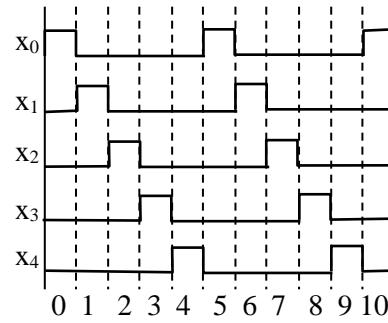

On connecte la sortie  $x_4$  d'un registre à 5 bits à son entrée u et on applique sur l'entrée de décalage D un signal d'horloge de période T. Représenter durant 10 périodes les signaux aux sorties  $x_0, \dots, x_4$  quand l'état initial est

a)  $x_0 = x_1 = x_2 = x_3 = 0$  et  $x_4 = 1$ .

b)  $(x_0, x_1, x_2, x_3, x_4) = (0, 1, 1, 0, 1)$ .

Un signal  $x_i$  est retardé d'une période par rapport à  $x_{i-1}$  et se définit par l'état initial du registre.

**EXERCICE 5-5**

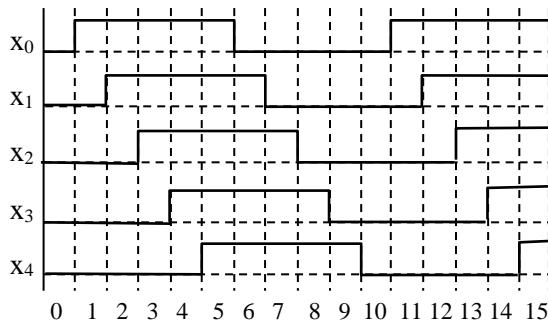

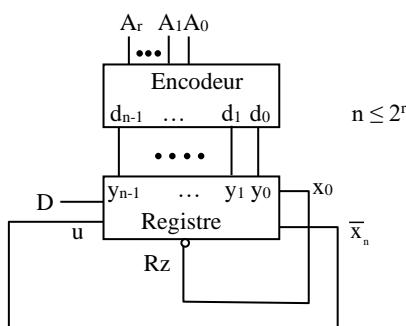

On connecte la sortie  $\bar{x}_n$  d'un registre à  $n$  bits à son entrée  $u$  et on applique sur l'entrée de décalage  $D$  un signal d'horloge de période  $T$ .

- Représenter les signaux aux sorties  $y_n, \dots, y_0$  en supposant qu'à l'instant initial  $y_n = \dots = y_0 = 0$ . Déduire que ce circuit peut être employé en diviseur de fréquence.

- Employer ce circuit et un encodeur pour obtenir un compteur modulo  $n$ .

a)

Si  $T$  est la période des impulsions sur l'entrée de décalage  $D$ , celle d'un signal  $x_i$  est  $nT$ . La fréquence du signal  $x_i$  est donc la division par  $n$  de la fréquence d'entrée.

b)

Le nombre d'impulsions sur  $D$  est égale à la position du 1 le plus significatif dans le registre et justement, par sa construction, l'encodeur associe un code binaire à cette position. Pour repartir de 0 quand ce nombre devient  $n$  c.à.d. quand  $x_0$  redévient 0, il suffit de connecter  $x_0$  à l'entrée  $Rz$  de remise à 0.

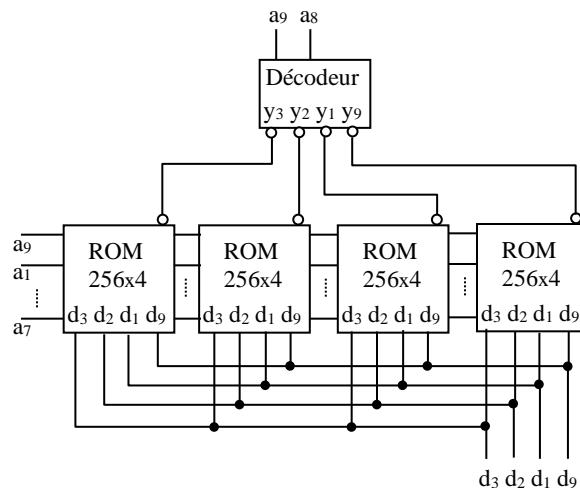

**EXERCICE 5-6**

Les mémoires ROM (programmables ou non) sont généralement munies d'une entrée d'activation CS

telle que pour  $CS = 0$  la mémoire fonctionne normalement et pour  $CS = 1$  toutes ses sorties deviennent flottantes. Utilisant 4 mémoires 256x4 et un décodeur construire une mémoire 1024x4.

La même adresse est appliquée à toutes les ROM. Comme pour  $CS = 1$  les sorties  $d_i$  d'une ROM sont flottantes, il est inutile d'employer des portes OR pour obtenir la réponse finale.

**EXERCICE 5-7**

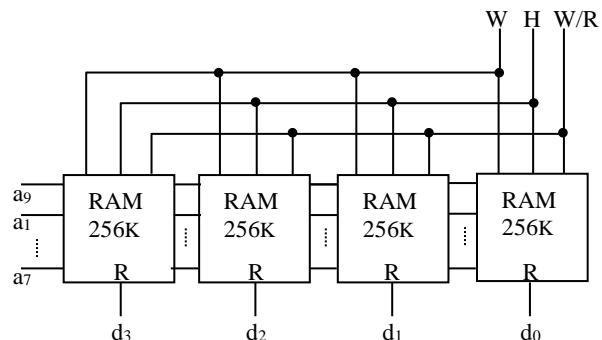

Comment connecter 4 RAM chacune de 256K pour constituer une RAM de 256K x 4 bits ?

La même adresse est appliquée à toutes les RAM qui sont commandées en parallèle. Les bits d'un mot sont à la même position dans les 4 RAM.

**EXERCICE 5-8**

- Est-ce que  $(0.6)_{10}$  peut avoir une représentation binaire exacte ?

- Convertir en octal ( $b = 8$ ) le nombre décimal  $(714.1875)_{10}$  et déduire ses écritures binaire et hexadécimale ( $b = 16$ ).

a)

$$0.6 \times 2 = 0.2 + 1$$

$$0.2 \times 2 = 0.4 + 0$$

$$0.4 \times 2 = 0.8 + 0$$

$$0.8 \times 2 = 0.6 + 1$$

$$0.6 \times 2 = 0.2 + 1$$

$\vdots$

$$\Rightarrow (0.6)_{10} = (0.100110011\dots)_2$$

On voit que la représentation binaire de  $(0.6)_{10}$  est nécessairement approximative.

b)

#### Conversion décimal-octal

| Partie entière          | Partie fractionnaire            |

|-------------------------|---------------------------------|

| $714 = 89 \times 8 + 2$ | $0.1875 \times 8 = 0.5 + 1$     |

| $89 = 11 \times 8 + 1$  | $0.5 \times 8 = 0 \times 8 + 4$ |

| $11 = 1 \times 8 + 3$   |                                 |

| $1 = 0 \times 8 + 1$    |                                 |

$$\Rightarrow (714.1875)_{10} = (1312.14)_8$$

#### Conversion octal-binaire

$$\begin{aligned}

(1312.14)_8 &= (2^3)^3 + 3(2^3)^2 + (2^3) + 2(2^3)^0 \\

&\quad + (2^3)^{-1} + 4(2^3)^{-2} \\

&= 2^9 + (2+1)2^6 + 2^3 + 2^1 + 02^0 \\

&\quad + 2^{-3} + 2^{-4} \\

&= (1011001010.0011)_2.

\end{aligned}$$

#### Conversion binaire-hexadécimal

$$\begin{aligned}

(1011001010.0011)_2 &= 2(2^4)^2 + 8(2^4) + 4(2^4) + 10 \\

&\quad + 2(2^4)^{-1} + (2^4)^{-1} \\

&= (2CA.3)_{16}

\end{aligned}$$

où  $A_{16} = (10)_{10}$  et  $C_{16} = (12)_{10}$ .

#### EXERCICE 5-9

Sachant que le complément-2 est égal au complément-1 + 1, déterminer le complément-2 de  $a = 01011000$ . Déduire une règle générale.

$$C1(a) = 10100111$$

$$\begin{array}{ccccccc}

1 & 0 & 1 & 0 & 0 & 1 & 1 & 1 \\

\Rightarrow C2(a) = + & & & & & & & 1 \\

\hline

0 & 1 & 0 & 1 & 1 & 0 & 0 & 0

\end{array}$$

Règle :  $C2(a)$  s'obtient en complémentant les bits de  $a$  situés après le premier 1 à partir de la droite.

#### EXERCICE 5-10

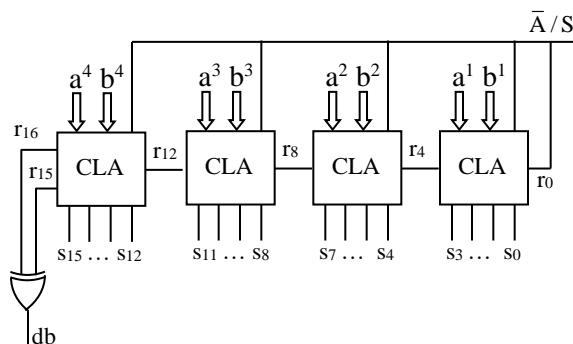

À l'aide de 4 additionneurs CLA à 4 bits chacun, construire un additionneur 16 bits en connectant un additionneur au précédent par la retenue finale de ce dernier. Comparer les durées de l'addition par le circuit ainsi obtenu et par l'additionneur à ondulation (16 addateurs complets en série).

Le temps  $t$  de l'addition par ce circuit est égal 4 fois le temps de propagation  $5t_p$  entre l'entrée  $r_k$  et la sortie  $r_{k+4}$  d'un CLA, d'où  $t = 20 t_p$  où  $t_p$  est le temps de propagation à travers une porte. Tandis que, pour un additionneur à ondulation de  $n = 16$  bits, ce temps vaut  $(2n + 1)t_p = 33t_p$  soit 1.65 fois plus lent que le circuit ci-dessus.

#### EXERCICE 5-11

Comparer la durée de propagation d'un additionneur à 2 niveaux avec celle d'un additionneur à 1 niveau. Chacun des additionneur comporte 4 CLA de 4 bits.

L'additionneur à 2 niveaux diffère de l'additionneur 1 niveau par la manière de calculer les retenues. Le  $k^{\text{ème}}$  CLA de ce dernier calcule sa retenue  $r_k$  en  $5t_p$  après le calcul de  $r_{k-1}$  par le CLA précédent. Le temps de propagation à travers un additionneur 1 niveau constitué de  $p$  CLA est donc  $t_1 = 5pt_p$ . Par contre, tous les CLA d'un additionneur 2 niveaux reçoivent simultanément les retenues  $r_{k-1}$  calculées en  $2t_p$  par un circuit combinatoire SP. Le temps de propagation à travers cet additionneur est donc  $t_2 = 2t_p + 5t_p = 7t_p$ , indépendamment du nombre  $p$  de ses CLA c.à.d. de la longueur des mots à additionner.

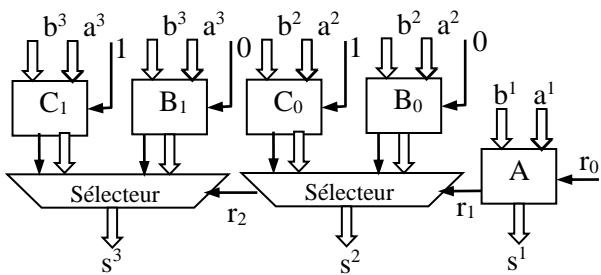

## EXERCICE 5-12

Considérons un additionneur à sélection de la retenue à 3 étages (figure ci-dessous). Soit  $t_p$  le temps de propagation d'une porte logique et admettons que le temps de propagation à travers le sélecteur est  $2t_p$ . Sachant que les additionneurs sont des CLA à 1 niveau, déterminer la durée de l'addition si

- a) A, B<sub>0</sub>, C<sub>0</sub>, B<sub>1</sub>, C<sub>1</sub> sont tous à 4 bits,

- b) A, B<sub>0</sub>, C<sub>0</sub> sont à 4 bits mais B<sub>1</sub> et C<sub>1</sub> sont à 5 bits.

Les 5 CLA répondent simultanément en  $5t_p$  quelles que soient les longueurs des mots qu'ils additionnent et le temps de propagation à travers un sélecteur est de  $2t_p$ . Ainsi, pour les deux cas a) et b),  $r_1$  et  $s^1$  apparaissent après  $5t_p$ ,  $r_2$  et  $s^2$  après  $5t_p + 2t_p = 7t_p$ ,  $r_3$  et  $s^3$  après  $7t_p + 2t_p = 9t_p$ .

## EXERCICE 5-13

Calculer le produit  $22 \times 30$  par multiplication séquentielle et le produit  $(-22) \times 30$  par l'algorithme de Booth.

### a) Multiplication séquentielle

b) Algorithme de Booth

## EXERCICE 5-14

Construire le tableau de la division itérative

$83 \div 14$ .

$m = 5$  et  $n = 2m - 1 = 9$ . La bascule  $F$  reçoit, après le décalage du registre  $P$ , son bit  $P_n$  de gauche puis, après le calcul de  $\Delta^k$ , elle reçoit le signe  $s$  de  $\Delta^k$ ,  $s = \text{reste}(\Delta^k) \oplus P_n$ .

| F | 0 | 1 | 1 | 1 | 0 | $\leftarrow 14$ | $\bar{s}$ |

|---|---|---|---|---|---|-----------------|-----------|

| s | 0 | 0 | 1 | 0 | 1 | 0               | 0         |

| D | 0 | 0 | 1 | 0 | 1 | 0               | 1         |

| - | 1 | 1 | 1 | 0 | 0 | 0               | 1         |

| D | 1 | 1 | 1 | 0 | 0 | 1               | 1         |

| + | 0 | 0 | 0 | 1 | 1 | 1               | 0         |

| D | 0 | 0 | 1 | 1 | 0 | 1               | 0         |

| - | 1 | 1 | 1 | 1 | 1 | 1               | 0         |

| D | 1 | 1 | 1 | 1 | 1 | 0               | 1         |

| + | 0 | 0 | 1 | 1 | 0 | 0               | 1         |

On voit que le quotient est  $q = 5$  et que le reste est  $r = 1 < 14$ .

EXERCICE 5-15

Représenter en simple précision les 4 modes d'arrondi de  $+(25.4)_{10}$  et de  $-(25.4)_{10}$ .

$$(25)_{10} = 2^4 + 2^3 + 2^0 = (11001)_2$$

$$0.4 \times 2 = 0.8 \pm 0, \quad 0.8 \times 2 = 0.6 \pm 1,$$

$$0.6x^2 = 0.2 \pm 1 \quad x^2 = 0.4 \pm 0$$

$$\Rightarrow (0.4)_{10} = (0.01100110\dots)_2.$$

Donc

$$(25.4)_{10} = (11001 \cdot 0110011001\dots)_2 \\ = (1 \cdot 1001 0110 0110\dots)_2^4$$

$$E = 4 + 127 = 131 = (2^7 + 2^1 + 2^0) \\ = (10000011)_2.$$

#### Arrondi par défaut

$$(25.4)_{10} = S | E | F$$

$$S = 0$$

$$E = 10000011$$

$$F = 1001 0110 0110 0110 0110 011$$

$$-(25.4)_{10} = S | E | F$$

$$S = 1$$

$$E = 10000011$$

$$F = 1001 0110 0110 0110 0110 100. (= M_{df} + 2^m)$$

#### Arrondi par excès

$$(25.4)_{10} = S | E | F$$

$$S = 0$$

$$E = 10000011$$

$$F = 1001 0110 0110 0110 0110 100.$$

$$-(25.4)_{10} = S | E | F$$

$$S = 1$$

$$E = 10000011$$

$$F = 1001 0110 0110 0110 0110 011.$$

#### Arrondi vers 0

$$(25.4)_{10} = S | E | F$$

$$S = 0$$

$$E = 10000011$$

$$F = 1001 0110 0110 0110 0110 011.$$

$$-(25.4)_{10} = S | E | F$$

$$S = 1$$

$$E = 10000011$$

$$F = 1001 0110 0110 0110 0110 011.$$

#### Arrondi au plus près

Avant le dernier 0, les bits de F sont égaux. Les fractions par excès et par défaut diffèrent par les 3 derniers bits et forment

$$m_{ex} = (100)_2 = 4 \text{ et } m_{df} = (011)_2 = 3$$

$$\text{Leur moyenne est } m_{moy} = 3.5 = (11.1)$$

Les 3 bits correspondants de la fraction réelle forment  $m = (11.0)_2 < m_{moy}$

$$\Rightarrow F = 1001 0110 0110 0110 0110 011 \\ \text{pour } (25.4)_{10} \text{ et } -(25.4)_{10}.$$

#### AUTRES EXERCICES ET COMPLÉMENTS

**5-16** Après chaque impulsion de l'horloge, un compteur synchrone passe à la valeur suivante de la séquence 0, 2, 4, 6, 1, 3, 5, 7, 0, 2, 4, ... . Pour réaliser ce compteur avec des bascules JK,

a) Dresser le tableau de l'état suivant en fonction de l'état actuel.

b) Dresser les tableaux des  $J_i$  et  $K_i$  des bascules et déduire ces fonctions.

c) Vérifier les résultats précédents en examinant la suite des mots binaires que doit produire le compteur

d) Représenter le circuit.

a)

La séquence 0, 2, 4, 6, 1, 3, 5, 7, 0, 2, 4, ... s'obtient en associant à l'état actuel  $(x_2 \quad x_1 \quad x_0)$  = 0 l'état suivant  $(x'_2 \quad x'_1 \quad x'_0)$  = 2, à l'état actuel 2 l'état 4, ... . Ceci se traduit par le tableau ci-contre.

|       | $x_2$   | $x_1$   |

|-------|---------|---------|

| $x_0$ | 2 6 1 4 | 3 7 0 5 |

b)

La transition de 0 = (0 0 0) à 2 = (0 1 0) se réalise en conservant l'état 0 des bascules 0 et 2 et en passant de l'état 0 de la bascule 1 à l'état 1. De même, pour effectuer la transition de 2 = (0 1 0) à 4 = (1 0 0), on conserve l'état de la bascule 0 et on complémentise les états de bascules 1 et 2. Ces transitions sont obtenues en appliquant aux entrées  $J_i$  et  $K_i$  des bascules les valeurs déduites du tableau suivant.

|                        |       |       |       |       |

|------------------------|-------|-------|-------|-------|

| $x_i \rightarrow x'_i$ | 0 → 0 | 0 → 1 | 1 → 0 | 1 → 1 |

| J K                    | 0 -   | 1 -   | - 1   | - 0   |

c)

#### Fonctions $J_i$ et $K_i$

| $J_0$ | $x_2$   | $x_1$ |

|-------|---------|-------|

| $x_0$ | 0 0 1 0 |       |

$$\Rightarrow J_0 = x_1 x_2$$

| $K_0$ | $x_2$ | $x_1$ |

|-------|-------|-------|

| $x_0$ |       |       |

$$K_0 = x_1 x_2$$

|       |            |       |

|-------|------------|-------|

| $J_1$ | $x_2$      | $x_1$ |

| $x_0$ | 1 1<br>1 1 |       |

|       |            |       |

$$\Rightarrow J_1 = 1$$

|       |       |       |

|-------|-------|-------|

| $K_1$ | $x_2$ | $x_1$ |

| $x_0$ |       | 1 1   |

|       |       |       |

$$K_1 = 1$$

|       |                 |       |

|-------|-----------------|-------|

| $J_2$ | $x_2$           | $x_1$ |

| $x_0$ | 0             1 |       |

|       | 0             1 |       |

$$\Rightarrow J_2 = x_1$$

|       |       |       |

|-------|-------|-------|

| $K_2$ | $x_2$ | $x_1$ |

| $x_0$ |       | 0 1   |

|       |       | 0 1   |

$$K_2 = x_1$$

c)

### Vérification

Le tableau ci-contre montre que  $x_0$  change de valeur seulement quand  $x_1 = x_2 = 1$  en un front d'activation par l'horloge. D'où  $J_0 = K_0 = x_1 x_2$ .  $x_1$  change de valeur à chaque front d'activation (bascule T). D'où  $J_1 = K_1 = 1$ .  $x_2$  change de valeur seulement quand  $x_1 = 1$  au front d'activation. D'où  $J_2 = K_2 = x_1$ .

| Nb | $x_2 x_1 x_0$ |

|----|---------------|

| 0  | 0 0 0         |

| 2  | 0 1 0         |

| 4  | 1 0 0         |

| 6  | 1 1 0         |

| 1  | 0 0 1         |

| 3  | 0 1 1         |

| 5  | 1 0 1         |

| 7  | 1 1 1         |

| 0  | 0 0 0         |

d)

### Circuit

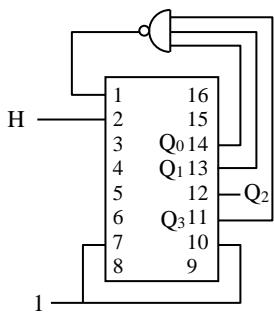

**5-17** Construire un décompteur synchrone modulo 10 ( $9 \rightarrow 8 \rightarrow \dots \rightarrow 0 \rightarrow 9 \dots$ ) qui, par une impulsion sur une entrée d'initialisation I, ramène l'état du décompteur à 9 à partir de tout autre état.

Ci-contre la matrice de transition qui donne, dans un tableau de Karnaugh, l'état suivant exprimé en decimal en fonction de l'état actuel exprimé en binaire

|       |                                                      |       |

|-------|------------------------------------------------------|-------|

| $x_1$ | $x_2$                                                | $x_3$ |

| $x_0$ | 9 7 3<br>1             5<br>2             6<br>0 8 4 |       |

|       |                                                      |       |

En appliquant aux entrées d'une bascule  $J_i K_i$  des tensions (0 ou 1) dépendantes de l'état actuel  $x$ , on passe de la composante  $x_i$  de  $x$  à la composante  $x'_i$  de l'état suivant  $x'$ . La relation entre une entrée  $(J_i, K_i)$  et  $x$  peut être donnée par 2 tableaux de Karnaugh. Comme  $x_0$  se modifie à chaque coup d'horloge, la bascule 0 doit se comporter en trigger en connectant ses entrées  $J_0$  et  $K_0$  à 1. Il reste à dresser les tableaux des  $J_i$  et  $K_i$ ,  $i = 1, 2$  et 3. Tenant compte du tableau des transitions précédent, à la case de 0 = (0, 0, 0) on associe dans les tableaux des bascules 1, 2 et 3 les couples  $(J_1, K_1) = (0, -)$ ,  $(J_2, K_2) = (0, -)$  et  $(J_3, K_3) = (1, -)$  car 9 = (1 0 0 1) et les transitions de  $x_1, x_2, x_3$  sont (0 → 0), (0 → 0) et (0 → 0). De même, la transition de 6 – (0 1 1 0) à 5 = (0 1 0 1) en associant aux entrées de bascules 0, 1, 2, et 3 les entrées  $(J_0, K_0) = (1, 1)$ ,  $(J_1, K_1) = (0, -)$ ,  $(J_2, K_2) = (-, 0)$ ,  $(J_3, K_3) = (0, -)$ . (Voir tableau à l'exercice 5-16)

|       |                   |                   |

|-------|-------------------|-------------------|

| $J_1$ | $x_2$             | $x_3$             |

| $x_1$ | 0 1             1 |                   |

| $x_0$ |                   | 0 0             0 |

$$\Rightarrow J_1 = (x_2 + x_3)\bar{x}_0$$

|       |                 |                 |

|-------|-----------------|-----------------|

| $K_1$ | $x_2$           | $x_3$           |

| $x_1$ |                 | 1             1 |

| $x_0$ | 0             0 |                 |

$$K_1 = \bar{x}_0$$

|       |                 |       |

|-------|-----------------|-------|

| $J_2$ | $x_2$           | $x_3$ |

| $x_1$ | 0 1             |       |

| $x_0$ | 0             0 |       |

$$\Rightarrow J_2 = \bar{x}_0 x_3$$

|       |                 |                 |

|-------|-----------------|-----------------|

| $K_2$ | $x_2$           | $x_3$           |

| $x_1$ |                 | 1             0 |

| $x_0$ | 0             0 |                 |

$$K_2 = \bar{x}_0 \bar{x}_1$$

|       |                 |       |

|-------|-----------------|-------|

| $J_3$ | $x_2$           | $x_3$ |

| $x_1$ | 1             0 |       |

| $x_0$ | 0             0 |       |

$$\Rightarrow J_3 = \bar{x}_0 \bar{x}_1 \bar{x}_2$$

|       |                 |                 |

|-------|-----------------|-----------------|

| $K_3$ | $x_2$           | $x_3$           |

| $x_1$ |                 | 1             0 |

| $x_0$ | 0             0 |                 |

$$K_3 = \bar{x}_0$$

D'autre part, le décompteur revient à 9 = (1001) à partir de tout autre état en appliquant la valeur logique 0 aux entrées Pr (preset) des bascules 0 et 3 et aux entrées Cr (clear) des bascules 1 et 2.

Tenant compte de cette remarque et des fonctions  $J_i$  et  $K_i$  obtenues ci-dessus, le circuit du décompteur synchrone avec une entrée de remise à la valeur initiale 9 est le suivant.

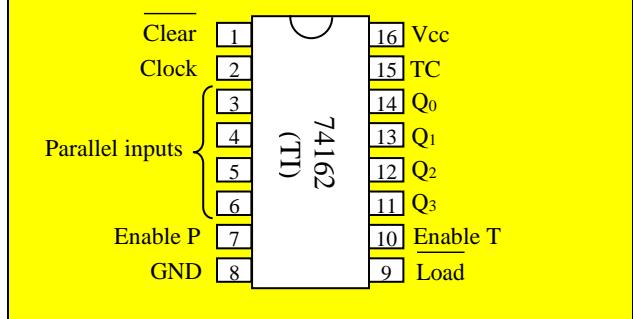

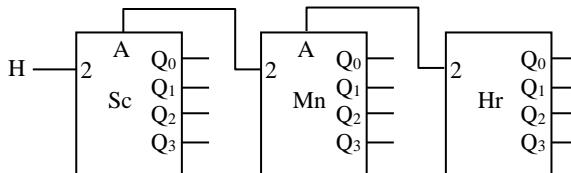

**5-18** La figure représente la puce d'un compteur BCD (modulo 10) complètement synchrone à front descendant (négative-going edge).

Les broches ont les rôles suivants :

- Un 0 sur la broche 1 annule les sorties  $Q_0$ ,  $Q_1$ ,  $Q_2$ ,  $Q_3$  au front montant de l'horloge.

- $(Q_3Q_2Q_1Q_0)_2$  est le nombre modulo 16 des impulsions de l'horloge qui arrivent à 2.

- Un 0 sur la broche 9 transmet, au front montant, le mot binaire placé sur les broches 3, 4, 5 et 6 aux sorties  $Q_0$ ,  $Q_1$ ,  $Q_2$  et  $Q_3$  dans cet ordre.

- Le compteur n'avance que si les broches 7 et 10 sont tous les deux à 1.

- La sortie 15 (terminal compte, TC) n'est égale à 1 que lorsque  $(Q_3Q_2Q_1Q_0)_2$  est à sa valeur maximum 9.

Utilisant deux puces 74162, l'un pour les unités et l'autre pour les dizaines,

- a) Construire pour les secondes ou les minutes d'une montre digitale un compteur de 00 à 59.

- b) Construire un compteur de 0 à 11 pour les heures de cette montre.

- c) L'horloge de cadence étant de 1 Hz, montrer les connexions entre les 3 compteurs : des secondes, des minutes et des heures.

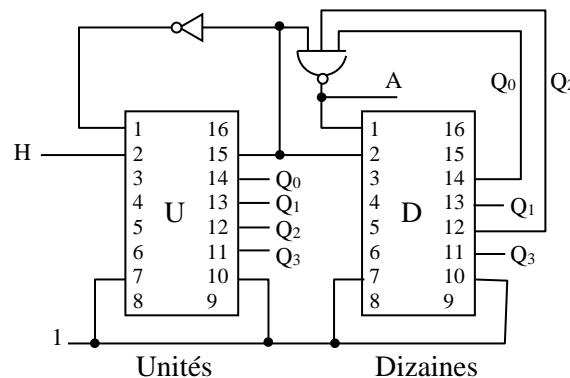

a) Compteur des secondes ou des minutes.

Admettons qu'à l'instant initial les deux compteurs sont mis à 0 par clear (1). Comme les entrées enable (7 et 10) des compteurs sont connectées à la tension  $V_{cc}$ , leurs sorties  $(Q_3Q_2Q_1Q_0)_2$  avancent de 1 à chaque impulsion sur leurs entrées d'horloge (2). Après 9 coups d'horloge H, la sortie TC (15) du compteur des unités U prend la valeur 1 qui s'applique à l'entrée (2) du compteur des dizaines D. En même temps l'entrée (1) de U s'annule ce qui annule ses sorties  $Q_3, \dots, Q_0$  ainsi que sa sortie TC. Cette dernière applique donc une impulsion sur l'entrée (2) de D dont la sortie avance de 1 et donne sur D

et U le nombre 10. Avec les nouvelles impulsions sur H on passe de 10 à 19 puis de 20 à 29, ... . Quand les deux compteurs arrivent à 59, la sortie TC de U et les broches Q<sub>2</sub> et Q<sub>0</sub> de D annulent à travers l'inverseur et la porte NAND, les entrées (1) des deux compteurs ce qui annule leurs sorties et le dénombrement recommence.

b) Compteur des heures

À chaque descente de H (2), la sortie (Q<sub>3</sub>Q<sub>2</sub>Q<sub>1</sub>Q<sub>0</sub>)<sub>2</sub> avance de 1. Quand cette sortie arrive à 11 = (1011)<sub>2</sub>, la porte NAND annule l'entrée 1 ce qui annule la sortie et le dénombrement recommence.

c) Montre digitale

Après 59 secondes, la sortie A à la sortie de la porte NAND du compteur des secondes Sc s'annule et, par l'entrée 2 du compteur des minutes Mn, elle avance la sortie de Mn de 1. Quand cette sortie arrive à 59, la sortie A de Mn s'annule et, par l'entrée 2 du compteur des heures Hr, elle avance la sortie de Hr de 1.

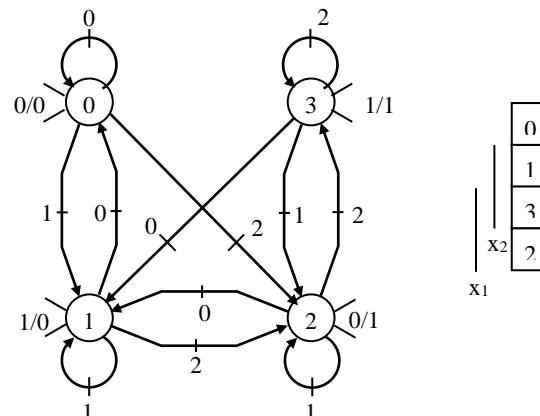

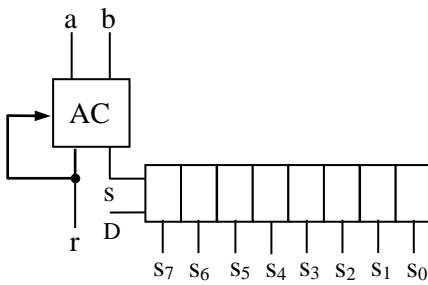

**5-19** Un additionneur série, synchronisé par une horloge, a deux entrées a et b et une sortie s. Chaque entrée reçoit successivement les bits d'un nombre et la sortie délivre successivement les bits de la somme des deux nombres. Réaliser cet additionneur en tant que machine de Moore et vérifier le résultat attendu.

À chaque itération, l'entrée est le couple (a, b) et la sortie est s/r où s est le bit de la somme à cette itération et r est son reste. En désignant par r<sup>-</sup> le reste à l'itération précédente et par u = a + b ∈ {0, 1, 2} la somme arithmétique on a :

$$s = \begin{cases} 0 & \text{si } u + r^- \in \{0, 2\}, \\ 1 & \text{si } u + r^- \in \{1, 3\}, \end{cases} \quad r = \begin{cases} 0 & \text{si } u + r^- \in \{0, 1\}, \\ 1 & \text{si } u + r^- \in \{2, 3\}. \end{cases}$$

Le diagramme de Moore est alors le suivant où les entrées sont les u et les sorties sont les s/r. À côté de ce diagramme, nous avons associé un état à chaque étape.

Ce diagramme se traduit par le tableau ci-contre montrant la transition de chaque état actuel  $x = (x_1, x_2)$  à l'état suivant  $x' = (x'_1, x'_2)$  en fonction de l'entrée (a, b).

|                | a | b |

|----------------|---|---|

| x <sub>2</sub> | 0 | 0 |

| x <sub>1</sub> | 0 | 0 |

|                | 1 | 1 |

| x <sub>2</sub> | 0 | 1 |

| x <sub>1</sub> | 0 | 1 |

|                | 1 | 0 |

| x <sub>2</sub> | 1 | 0 |

| x <sub>1</sub> | 0 | 1 |

|                | 1 | 1 |

| x <sub>2</sub> | 1 | 1 |

| x <sub>1</sub> | 1 | 1 |

|                | 0 | 0 |

La composante  $x'_i$ ,  $i = 1, 2$ , de l'état suivant s'obtient en remplaçant chaque chiffre du tableau de transition par la composante  $x_i$  de l'état de l'étape vers laquelle le système se dirige. On obtient les tableaux suivants.

|                | a | b |

|----------------|---|---|

| x <sub>2</sub> | 0 | 0 |

| x <sub>1</sub> | 0 | 0 |

|                | 1 | 1 |

| x <sub>2</sub> | 0 | 1 |

| x <sub>1</sub> | 0 | 1 |

|                | 1 | 1 |

| x <sub>2</sub> | 1 | 0 |

| x <sub>1</sub> | 0 | 1 |

|                | 1 | 0 |

| x <sub>2</sub> | 1 | 1 |

| x <sub>1</sub> | 1 | 1 |

|                | 0 | 0 |

|                | a | b |

|----------------|---|---|

| x <sub>2</sub> | 0 | 1 |

| x <sub>1</sub> | 0 | 1 |

|                | 1 | 0 |

| x <sub>2</sub> | 1 | 0 |

| x <sub>1</sub> | 0 | 1 |

|                | 1 | 0 |

| x <sub>2</sub> | 1 | 0 |

| x <sub>1</sub> | 0 | 1 |

|                | 1 | 0 |

De ces tableaux, on déduit les relations suivantes :

$$\begin{aligned}x'_1 &= ab + x_1(a+b) = ab + x_1(a \oplus b + ab) \\&= ab + x_1(a \oplus b).\end{aligned}\quad (1)$$

$$\begin{aligned}x'_2 &= \bar{x}_1(\bar{a}b + a\bar{b}) + x_1(\bar{a}\bar{b} + ab) \\&= x_1 \oplus a \oplus b.\end{aligned}\quad (2)$$

Or d'après le diagramme et le codage des étapes,

$$r = \bar{x}_1 x_2 + x_1 x_2 = x_2,$$

$$s = x_1 \bar{x}_2 + x_1 x_2 = x_1.$$

Comme attendu, on voit, d'après (1) et (2) que l'état suivant d'un additionneur série est la sortie ( $s, r$ ) d'un addeur complet. Il suffit d'ajouter à cet addeur un registre pour compléter le circuit d'un additionneur série.

**5-20** Utilisant un registre à 4 bits et une porte XOR,

a) construire un circuit synchrone dont l'état suivant  $x'$  est lié à l'état actuel  $x$  par les relations :

$$x'_3 = x_1 \oplus x_0, \quad x'_2 = x_3, \quad x'_1 = x_2, \quad x'_0 = x_1. \quad (1)$$

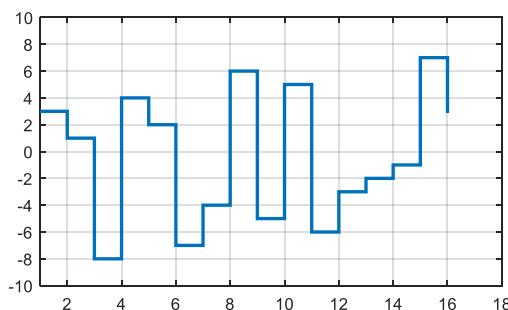

b) La suite des valeurs signées de  $(x_3 x_2 x_1 x_0)_{c2}$  constitue ce qu'on appelle un *signal pseudo-aléatoire*. Écrire et représenter cette suite partant de la valeur +3.

c) Soit  $x' = Tx$  la forme matricielle des relations (1) où  $T$  est la transformation qui associe à un vecteur  $x$  appartenant à l'espace  $\mathcal{B}^4$  muni des opérations logiques  $\cdot$  et  $\oplus$  le vecteur  $x'$ . Calculer  $T^2$ ,  $T^3$ ,  $T^5$  et  $T^{15}$ . Pour  $x = (0 \ 0 \ 1 \ 1)$ , calculer  $T^2x$ ,  $T^3x$ ,  $T^5x$  et  $T^{15}x$  et vérifier ces calculs en se référant à b).

a)

b)

|      |    |      |    |      |    |      |    |      |    |      |    |

|------|----|------|----|------|----|------|----|------|----|------|----|

| 0011 | +3 | 0100 | +4 | 1100 | -4 | 0101 | +5 | 1110 | -2 | 0011 | +3 |

| 0001 | +1 | 0010 | +2 | 0110 | +6 | 1010 | -6 | 1111 | -1 |      |    |

| 1000 | -8 | 1001 | -7 | 1011 | -5 | 1101 | -3 | 0111 | +7 |      |    |

Partant de +3, on obtient le signal suivant en 15 périodes d'horloge.

c)

$$T = \begin{pmatrix} 0 & 0 & 1 & 1 \\ 1 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 \\ 0 & 0 & 1 & 0 \end{pmatrix} \quad T^2 = \begin{pmatrix} 0 & 1 & 1 & 0 \\ 0 & 0 & 1 & 1 \\ 1 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 \end{pmatrix}$$

$$T^3 = \begin{pmatrix} 1 & 1 & 0 & 0 \\ 0 & 1 & 1 & 0 \\ 0 & 0 & 1 & 1 \\ 1 & 0 & 0 & 0 \end{pmatrix} \quad T^5 = \begin{pmatrix} 0 & 1 & 0 & 1 \\ 1 & 0 & 1 & 1 \\ 1 & 1 & 0 & 0 \\ 0 & 1 & 1 & 0 \end{pmatrix}$$

$$T^{15} = T^5 T^5 T^5 = \begin{pmatrix} 1 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 \\ 0 & 0 & 1 & 0 \\ 0 & 0 & 0 & 1 \end{pmatrix}$$

Vérification

$$\begin{aligned}Tx &= (0 \ 0 \ 0 \ 1), \quad T^2x = (1 \ 0 \ 0 \ 0), \quad T^3x = (0 \ 1 \ 0 \ 0) \\T^5x &= (1 \ 0 \ 0 \ 1), \quad T^{15}x = (0 \ 0 \ 1 \ 1).\end{aligned}$$

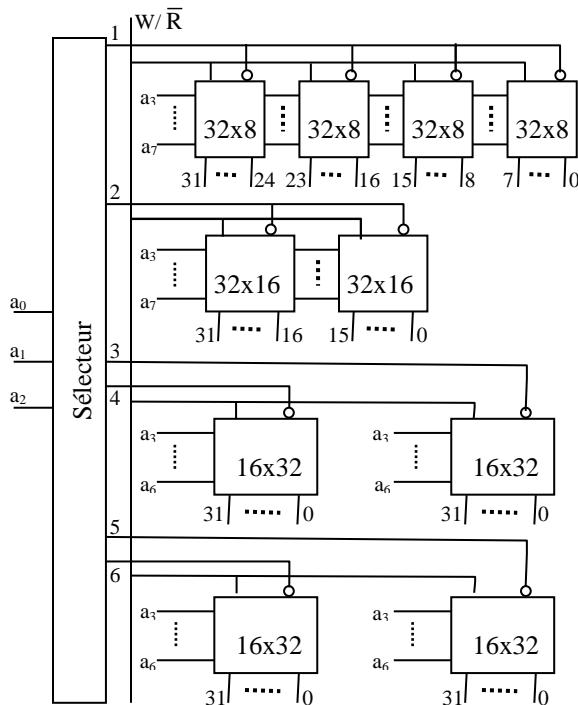

**5-21** Construire une mémoire RAM de 128Mx32 bits utilisant 4 RAM de 32Mx8 bits, 2 RAM de 32Mx16 bits et 4 RAM de 16Mx32 bits et un

circuit de décodage. Chaque RAM comporte les 2 broches  $\overline{CS}$  (chip select), R /  $\overline{W}$  (read/write)

Les 4 RAM 32Mx8 bits connectées à la même adresse constituent une RAM A de 32Mx32 bits.

Les 2 RAM de 32Mx16 bits connectées à la même adresse constituent une autre RAM B de 32Mx32 bits.

Chacune des RAM  $C_1, C_2, C_3, C_4$  a sa propre adresse.

Un sélecteur active l'une des RAM A, B,  $C_1, \dots, C_4$ . On obtient ainsi une RAM de 128Mx32 bits ( $32 + 32 + 4 \times 16 = 128$ ). Par exemple pour lire ou écrire un mot dans B, on l'adresse par  $(a_7, \dots, a_3, 0, 1, 0)$  où  $(a_7, \dots, a_3)$  est l'adresse des 16 bits supérieurs et 16 inférieurs du mot.

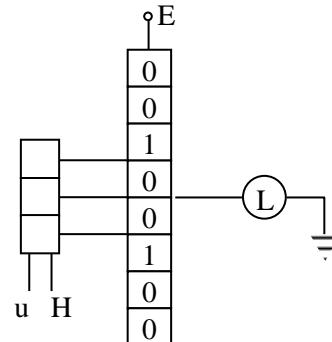

**5-22** Une lampe L s'allume ou reste allumée si aux 3 derniers fronts d'activation de l'horloge les valeurs d'un signal u sont alternées (010 ou 101). Construire pour ce système une machine synchrone en n'utilisant qu'un PROM et un registre. Comparer avec les circuits de l'exemple 4-6.

Les 3 dernières valeurs de u, introduites dans un registre à 3 bits, sont employées comme l'adresse

d'une PROM de 8 mots chacun de 1 bit. En programmant cette mémoire, il suffit d'associer aux adresses 2 = (010) et 5 = (101) la donnée 1 et aux autres adresses la donnée 0. La lampe lit le bit de adressé.

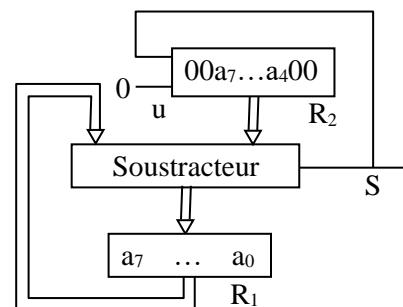

### 5-23 Montrer que

$$(a_7 \dots a_0)_{BCD} = (a_7 \dots a_0)_2 - 6(a_7 \dots a_4)_2$$

et construire un convertisseur BCD → binaire à 8 bits utilisant un soustracteur et deux registres 8 bits.

$$\begin{aligned} (a_7 \dots a_0)_{BCD} &= 10(a_7 \dots a_4)_2 + (a_3 \dots a_0)_2 \\ &= 2^4(a_7 \dots a_4)_2 + (a_3 \dots a_0)_2 - 6(a_7 \dots a_4)_2 \\ &= (a_7 \dots a_0)_2 - 6(a_7 \dots a_4)_2. \end{aligned}$$

Sachant que  $6 = 2^2 + 2$ , l'égalité précédente s'écrit

$$\begin{aligned} (a_7 \dots a_0)_{BCD} &= (a_7 \dots a_0)_2 \\ &\quad -(00a_7 \dots a_4 00)_2 - (000a_7 \dots a_4 0)_2 \end{aligned}$$

Une réalisation simplifiée est la suivante.

Initialement, on introduit les nombres  $(a_7 \dots a_0)_2$  et  $(00a_7 \dots a_{400})_2$  respectivement dans les registres  $R_1$  et  $R_2$ . Une première impulsion sur  $S$  effectue la soustraction de ces deux nombres, place le résultat dans  $R_1$  et décale  $R_2$  vers la droite en introduisant à gauche un 0. Une deuxième impulsion sur  $S$  soustrait  $R_2$  de  $R_1$  et donne le résultat final dans  $R_1$ .